## **Dot Matrix LCD Character Modules**

### **Application Notes**

#### Table of Contents

- 1. SELECTING AN LCD MODULE

- A. Introduction

- B. Fluid Types

- C. Viewing Modes and Colors

- D. <u>Backlighting</u>

- 1. EL Backlit

- 2. LED Backlit

- 2. HARDWARE DESIGN

- A. Power Supply Requirements

- B. Temperature Compensation

- C. Interface

- D. Unique Timing Aspects of A/N LCDs

- E. Mounting Suggestions

#### 3. SOFTWARE REQUIREMENTS

- A. Introduction

- B. Initialization

- C. 4-bit Operation

- D. Display Addressing

- E. Specially Coded Displays

- F. Instruction Table

- G. Instruction Description

- H. Use of CG RAM

- 4. APPENDIX

- A. Designers Checklist

- B. Precautions for Handling and Operating LCD Modules

- C. Troubleshooting Guide

- D. Timing Diagrams

- E. Font Chart

- F. Processor Specific Interface Suggestions

- G. Polarizer Type Summary

## I. SELECTING an LCD MODULE

### A. INTRODUCTION

Selecting an LCD module involves 2 basic design decisions. 1) What size and format is required to display the desired information. 2) What optical characteristics will look best in the package and attract the user to the product. Densitron produces dot-matrix LCDs in two formats: fully functional, Alphanumeric Modules; and fully-populated Graphic modules. This set of application notes is for use with the alphanumeric (A/N) or character type modules. Refer to separate specifications and application notes for operating graphic modules.

Alpha-numeric modules display characters, numerals, symbols and some limited graphics. Interface is achieved via a bi-directional, parallel ASCII data bus. Necessary features such as Character Generation, Display RAM Addressing, Cursor Scrolling, Blanking, and Handshake are all included. User programmable fonts are supported. In summary, these modules are the simplest and most economic means to communicate meaningfully between any micro-system and the outside world. Their inclusion adds to any product's appeal.

Alpha-numeric modules range from 8 to 80 characters per line. One, two or four character lines may be chosen. Character height spans 0.130" (3.31 mm) to 0.500" (12.71 mm). Most formats are available in a variety of packages to meet various mounting requirements. Multi-line models offer the best value when analyzed by a "cost per character" basis. Displays are readable both day and night by selecting a backlight option. Extended temperature modules are available which operate between -20 and +70C.

For requirements of more than 4 lines or 40 characters across, select a graphic formatted module. Graphic modules are also used when different sized characters are needed, and when special fonts such as Chinese or Arabic are required.

Selecting the exact version of an LCD once the format is decided is largely a subjective judgement. Color, fluid type, and backlighting determine the overall look of the display and often the appearance of the end product. Operating conditions such as temperature, lighting conditions, and available power are also factors in determining the type of display to use.

The following sections explains the optical characteristic options available in A/N modules,

### **B. FLUID TYPES**

The fluid type determines the contrast ratio, viewing angle, and temperature range of an LCD. Densitron uses 3 basic classes of fluid, TN (Standard type), NTN (high contrast type), and STN (premium high contrast type). Many TN and NTN models are available in extended temperature range. Contact Densitron for current availability.

#### **TN Fluid**

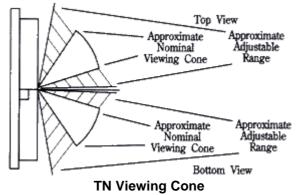

TN Fluid is the least expensive type. The viewing angle is about 40-45, and must be designated "top" or "bottom" view preference. Bottom view is used when the user will be below the plane perpendicular to the display, such as on a desk calculator. Top view is used when the display is mounted on a vertical surface below eye level. See diagram below.

#### STN AND NTN Fluid

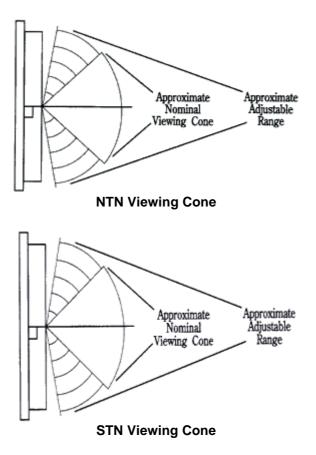

STN and NTN are both high contrast and wide viewing angle fluids. They differ in the level of contrast and viewing angle they achieve. Both can be seen above and below the plane perpendicular to the display. See the diagram below.

The vertical viewing cone on all fluids can be adjusted by controlling the VO voltage. The range of adjustment is shown in the viewing angle charts below. The horizontal cone is relatively fixed.

| Fluid Type | Typical Contrast Ratio | Typical Viewing Angle |

|------------|------------------------|-----------------------|

| TN         | 3:1                    | 40-45°                |

| NTN        | 7:1                    | 60°                   |

| STN        | 10:1                   | 75°                   |

### C. VIEWING MODES

The fluid type, polarizers and module construction determine the viewing mode and colour of the display. Displays are either "postive image", dark characters on a light background; or "negative image", light characters on a dark background. Backlight capability is determined by the presence or absence of a reflector or transflecter on the back side of the glass.

Reflective displays have a full reflector. The cannot be backlit. They offer the lowest power option and the best contrast in high ambient light conditions. They are not available in "positive image".

Transmissive displays are usually negative image and are backlit for best readability. They can be used in well lit indoor conditions to dark environments, typically not recommeded for daylight usage. They offer a different appearance than typical LCDs, bringing a light emitting look to the product.

Transflective displays combine the features of reflective and transmissive modes. These positive image displays can be read in all lighting conditions. The backlight can be turned on for low light levels or operated continuously to add the light-emitting look to a product.

#### Colors

TN positive image displays will have a silver/grey background and dark, almost black characters. In the negative image, the background will be black and the characters will be the color of the backlight, usually yellow/green or white. (See section on backlighting).

NTN and STN positive image displays can have a silver or yellow background with dark characters. Negative image versions have a dark blue background, characters are the folour of the backlight.

Choice of color is determined by what fits best in the package. Not all NTN displays are available in all colors. Consult Densitron for current availability.

## D. BACKLIGHTING CHARACTER MODULES

Backlighting is used on LCDs to make them readable in low light conditions and to add te "pizazz" that a light-emitting display gives a product. Refer to the section on viewing modes for the types and applications of display that are backlit. Densitron currently uses 2 methods to backlight character LCD module: Electroluminescent (EL) and Light Emitting Diode (LED). Selection depends on desired color, available power, and required life.

#### 1) EL Backlighting

EL backlighting is the original LCD backlight. It is thin, lightweight, low power, and fits between the glass assembly and PCB without any modification to the module. Most positive mode displays are furnished with a blue green lamp. Negative mode displays usually come with a white lamp. Other colors can be specially ordered.

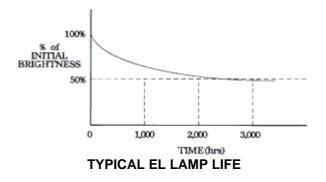

EL lamps operate from an AC power source, typically 400Hz at 70-110 VAC. Densitron supplies a full range of DC to AC inverters to power the lamps from a +5VDC source. There is no hard and fast rule for matching an inverter to a specific lamp. Lamp brightness and life are inversely proportional. That is the harder the lamp is driven the brighter it will be, but the shorter the life. Under rated operating conditions lamp life is about 2,000 to 2,500 hours to half its original brightness. Operating conditions such as temperature and humidity will also effect lamp life. The graph below illustrates the brightness vs life curve.

Recommended inverters for various sizes of modules are shown below. Design considerations such as the operating conditions, desired brightness, required light, and lamp life must be balanced when designing with EL backlighting. For example, a negative transmissive display used in normal room lighting

may look better when driven with a larger inverter but useful life will be shortened.

| Inverter Model | Displays                                                  |

|----------------|-----------------------------------------------------------|

| DAS5V4         | All A/N Displays except 4x40, 2x40, LM300 & LM4700 Series |

| DAS5V7         | 4x40, 2x40, LM300 & LM700 Series Transflective            |

| DAS5V8         | 4x40, 2x40, LM300 & LM700 Series Transflective            |

**Inverter Recommendations**

#### 2) LED Backlighting

LED backlighting offers a significant life advantage over EL lamps, but at the sacrifice of power and module size. Lamp life is in excess of 50,000 hours, and in most cases, 1 lamp failing does not make the backlight unusable. LED backlit does not make the backlight unusable. LED backlit modules are 2-4mm thicker than an EL or non-backlit module. Standard color is yellow-green. Red amber and other colors may be specially ordered.

LED Backlight Functional Diagram

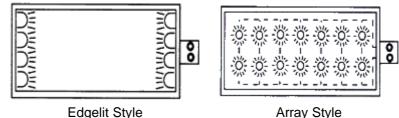

Densitron offers two types of LED backlights; edgelit and array. Their basic format is shown above.

Edgelit can be used on modules up to 20 characters wide. Beyond 20 characters, the middle of the display begins to dim when compared to the edges. (The LM43X series uses a top mounted edgelight to achieve its balance of light and power). Edgelight is the lower power of the two types. The 4XXX series edgelit modules typically operate 30 to 60mA(at +5VDC) and come with a built in current limit resistor. The 43X series is somewhat higher and must have a limited resistor in series for proper operation.

Array backlighting produces a brighter and more even light. Power is the main consideration when designing with this type of module. It is not recommended for battery powered applications where the lamp will be on all the time. (It may be suitable for "on demand" applications).

Limit resistors must be used for array backlit modules and the LM43X series. Refer to the specific module specification for recommended and/or maximum backlight ratings. LEDs are arranged in serial pairs and operated in parallel (see diagram). The lamp will require 4.2VDC. Brightness can be set or controlled by selecting the proper limit resistor. Select a resistor that will drop the remaining voltage at the desired current. For example, if 200mA produces the desired brightness and the supply voltage is +5VDC, the limit resistor will drop 0.8VDC (5.0 - 4.2). Therefore, E/I = R = 0.8/0.2 - 40hms.

Variable brightness can be controlled with a digital potentiometer or pulse-width modulated circuit.

## **II. HARDWARE DESIGN**

### A. POWER SUPPLY REQUIREMENTS

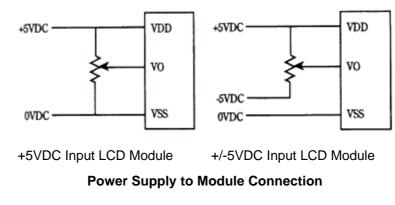

Modules require +5V at 1 to 10 milliamps. Extended temperature and some high contrast modules require -5V, also at low current. Inexpensive ICs convert +5V to -5V efficiently. If the display has backlighting, required power must also be budgeted. The power supply does not have to "lock-on" +5V but it must not "spike" beyond the module's absolute maximums.

A module's logic circuits have 3 connections to the power supply: VDD (+5VDC); VSS (Ground); and VO, viewing angle adustment, sometimes called contrast or bias control. The diagrams below show typical

connections. Contrast can also be controlled digitally with a digital potentiometer or DAC.

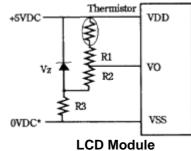

### **B. TEMPERATURE COMPENSATION**

LCD modules have a limited operating temperature range. (See exact model for specific limits). The fluid within the glass is the most limiting factor. Over the rated range, the bias, or VO voltage required to optimise the contrast and maintain a constant viewing cone varies slightly. Compensation or adjustment can be achieved manually, with a tem-erature compensation circuit, or a combination of both.

Manual adjustment involves user accessible control via a potentiometer or digital device as explained above. A standard, negative temperature coefficient thermostat serves as an inexpensive, automatic sensor. It should be mounted as close to the glass as possible to get an accurate measurement. A thermistor circuit can be configured to provide automatic temperature compensations. Each module's specification lists approximate VO voltages required at the extremes of the temperature range and at 25C. A suggested circuit is shown below.

When operating outside of the module's rated temperature range, forced air and/or a heater are required to maintain reliable operation. The heater manufacturer can offer design assistance.

\*For displays requiring -5VDC, R3 should be connected to -5, VSS to ground. Temperature Compensation Circuit Example

Notes:

1) Typical termistor value 15k @ 25C, B=4300

2) R1 and R2 values are selected based on required VO level. See module specifications.

3) R1 and R2 can be variable resistor for manual control.

4) Vz value = 4.5V for1/8 & 1/11 duty cycle displays: 5.0V for 1/16 duty cycle; 10V for modules using +/-5V supply.

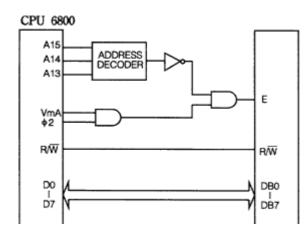

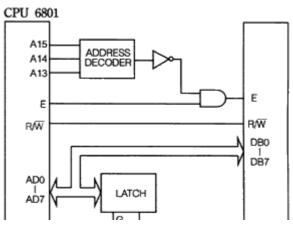

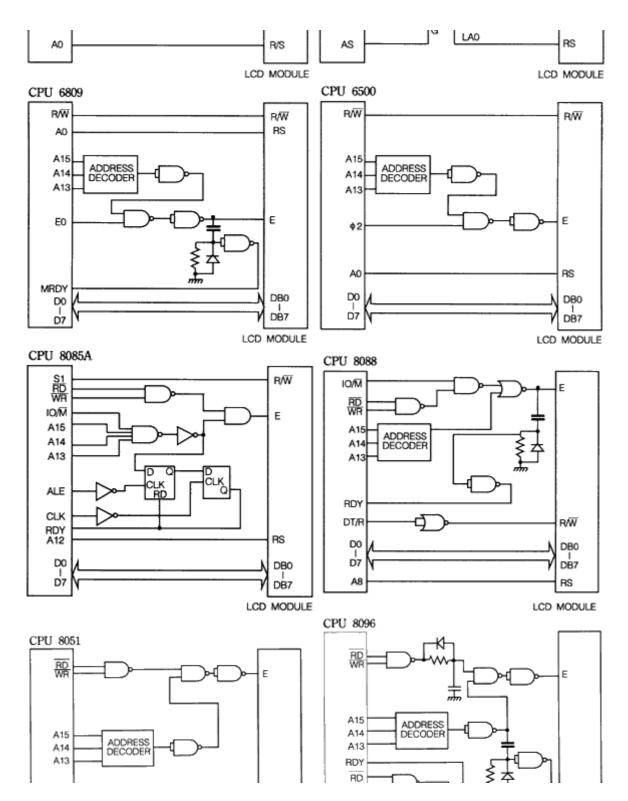

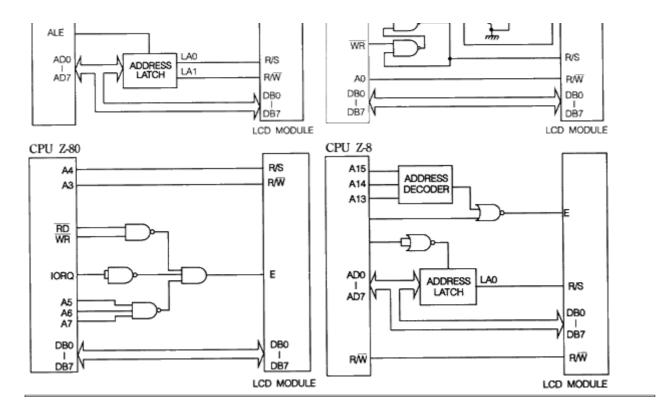

### C. INTERFACE

A/N modules are an intelligent peripheral which can communicate, bi-directionally, within the master system. Tie the device into the system data bus and treat it as RAM, I/O, or expanded, parallel I/O. The module is "selected" by gating a decoded, "module-address" output, with the host processor's "read or write" strobe. The resultant signal, applied to the LCDs "enable" input, clocks in data. There is no conventional "chip-select".

Interfacing the module to an existing micro-system involves:

- a) joining the module to the host's data bus.

- b) developing a "strobe" signal for the "E" signal

- c) applying appropriate signals to modules "RS" and "R/W"

- d) applying the proper "viewing angle" voltage to the display's VO pin.

Suggested interface circuits for most popular microprocessors are whoe on pages 16 and 17.

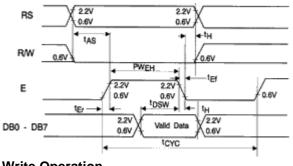

### D. UNIQUE TIMING ASPECTS OF A/N LCDs

LCD modules provide a complete display subsystem which must be properly interfaced to the host microcomputer. The modules are classified as a "slow" periphera. Both access and strobe times exceed those normally encountered. A successful marriage requires strict attention in detail.

The Enable ("E") signal is the key signal line. This signal "clocks" the data and control signals into the LCD's internal microcontroller. The "E" signal must be a clean, positive going, digital strobe, which is active while data and control information are stable and true. The modules do not have a chip select line and so a decoded, host "select" signal must be geared with a proper strobe to generate this "E" signal. All module timing is referenced to specific edges of the "E" signal. The "E" signal is applied only when a specific module transaction is desired.

The "E" strobe must be 450 nS wide, minimum. It has a minimum period of 1000nS. The "E" line would only be pulsed this often during a "read" of the busy flag, performed during a "polled" display routine. Normally "E" strobes would be approximately 40 microseconds apart - which is the maximum display throughput. (See Instruction Table for complete list of execution times).

The 2 control lines, RS and R/W, must set-up 140 nS prior to the activation, or rise, of "E". These signals must remain stable, and hold for 10nS at the fall of "E". When a parallel port supplies RS, R/W and "E", do not allow these lines to all change together. This would result if a single instruction was employed and would surely violate the set-up requirement. Instead a second instruction must independently set the "E" bit high, after RS and R/W have been set. When the "E" signal is derived from a host strobe signal, it is only necessary to choose address or control signals which meet the 140nS demand. A single instruction transfer would be perfectly valid in this case - and is the goal.

When the host outputs RD and WR strobes these should not be linked to the module's R/W line. Since this same signal provides the "E" signal a set-up violation will occur. In this case it is preferable to use an address bit which sets-up earlier in the host's machine cycle. This is a crucial point.

The data bus must set-up 195 nS prior to the fall of "E". Atain these lines must hold for at least 10nS after "E" falls. Most host strobes should meet these requirements without difficulty.

The classic problem is encountered when the host micro is running so fast that the strobes are too narrow (450nS) to serve as the "E" pulse. In this case: a) prolong thewe pulses by using the host's "ready" input, b) prolong by employing that mode which extends timing, or c) decrease the host's crystal frequency. When these options are not viable it will be necessary to latch both the data and control information and then activate the "E" signal.

Timing diagrams and suggested interfaces to various common microprocessors are in the appendix.

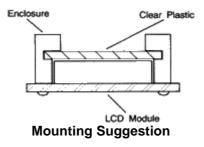

### **E. MOUNTING SUGGESTIONS**

Care must be taken when mounting an LCD module to ensure that module is not stressed when installed and the surface is not exposed to scratches or harmful material.

Causing any kind of warp on the PCB of the module may product open columns or rows of dots, or intermittent display. Presure on the bezel from the top or against the bezel tabs will lead to similar

#### problems.

The front surface of the module is a sensitive plastic polarizer, not glass. Liquid must not be allowed to condense upon the device. Whenever possible, install an optically correct "protection Barrier" between the outside world and the display. This should be a non-polarized plastic or polycarbonate, which will reduce the incidence of foreign-object invasion and static discharge into the display. To keep glare at a minimum, mount the protective piece as close to the display surface as possible while preventing pressure on the piece from being transmitted to the LCD. Non-glare properties can be added to the protective piece at a slight loss of display clarity.

## **III. SOFTWARE REQUIREMENTS**

### A. INTRODUCTION

Software determines what, how and where data is displayed on the LCD. All Densitron character modules feature the Hitachi HD44780 or equivalent controller IC. This versatile chip features:

- Built-in character generator with 192 character modified ASCII character set.

- Ability to program up to 8 custom characters.

- Bi-directional 8 or 4 bit bus interface

- 80 character RAM

- Automatic reset on power up

- Wide range of instruction functions including:

- Display clear, Cursor positioning, Display or cursor shift on data entry, and Display ON/OFF

Instructions are explained in detail on the following pages.

### **B. INITIALIZATION**

The module has 2 registers; one for inputting instructions and one for reading or writing data. Instructions are used to tell the module how and where to put the data. If the rise time of the power supply meets the criteria below, the module will default to the following functions via an internal initialization routine:

- Clear Display

- Function Set DL=1: 8 bits interface

- N=0: 1 line display

- F=0: 5x7 dot font

- Dislay ON/OFF control D=0: Display OFF

- C=0: Cursor OFF

- B=0: Blink OFF

- Entry Mode Set I/O=1: +1 increment

- DD RAM is selected

The display will be busy for approximately 15mS after power ON.

Power Supply Timing Requirements for Internal Initialization

If power supply rise time cannot be assured of meeting the requirements above, or if different parameters are required (such as for a 2 line display), an initialization routine will have to be sent from the host. When first setting up the display, Densitron recommends the following initialization routines for 8 bit interfaces:

- 1 line display with 5x7 font:

- 30, 30, 06, OE, 01 (hex)

- 1 line display with 5x10 font:

- 34, 34 ,06 ,OE, 01 (hex)

- 2 line display with 5x7 font:

- o 38, 38, 06, OE, 01 (hex)

Wait states should be programmed to allow 15mS after power up before initialization begins. Waiting 4.1mS between the "3X" codes and 100S after the second "3X" code add a safety margin and ensure proper initialization.

After sending this routine, you should have a clear display with a flashing cursor in the upper left position. The cursor will then increment to the right with each data RAM write command. If, you do not have this display, see Troubleshooting Tips in the appendix.

### **C. 4-BIT OPERATION**

The modules will operate from a 4-bit wide data bus. Data is transferred over data lines D7-D4. D3-D0 may float. 8-bit hex code is sent one nibble at a time, with the most significant nibble sent first. The function set in the initialization routine must change to accommodate this mode. A recommended initialization routine is as follows:

2 line display with 5x7 font:

2, 8, 2, 8, 0, 6, 0, E, 0, 1(hex)

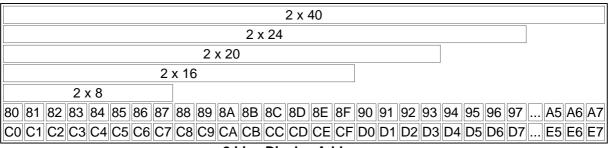

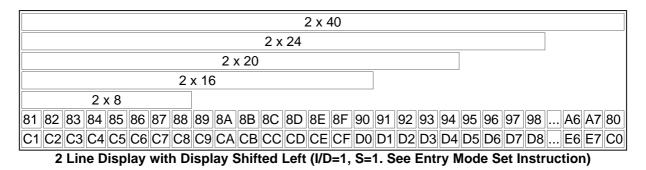

### D. DISPLAY ADDRESSING

The display RAM is 8 characters. If the display is less than 80 characters, what is on the screen is a "window" on the RAM. What is displayed depends on the Entry Mode Set instruction. Address diagrams on the next page show RAM addresses as they appear after a Clear Display or Return Home instruction, or when Entry Mode Set instruction S=0.

If a 2-line display has less than 40 characters per line, the cursor will advance off the screen after the last character of the first line. To put data on the secone line, a Set DD RAM Address instruction must be sent.

When instruction S=1, the display is shifted. This makes the characters look as though they are marching across the screen on entry. It also lets small displays (2x16s, for example) to have data stored in non-visible areas of the RAM and shifted in to view with one command. The last diagram shows how the addresses "wrap" in this mode.

### E. SPECIALLY CODED DISPLAYS

Three types of displays have different addressing than typical 1 or 2 line displays. They are:

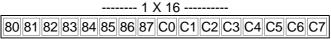

- 1. 1 chip 1 line by 16 character displays

- 2. 4 line by 16 or 20 character displays

- 3. 4 line b 40 character displays

**1 chip 1x16** - The HD44780 has the ability to control up to 16 characters without any other driver ICs. A lower cost 1 line by 16 character display can be manufactured to take advantage of this feature. To do this, it is necessary to initialize the display in the 2 line mode. The display is then addressed as a 2 line display. Line 1 addresses the first 8 characters; line 2, the second 8. When the cursor gets to the ninth character of the first line, it will "disappear" into undisplayed RAM (assuming no display shift). A Set DD RAM Address must be sent to reposition the cursor to the ninth displayed character which is logically the first position of the second line.

#### 1 Chip 1x16 Addresses

**4x40** - The maximum capacity of the HD44780 is 80 characters. The 160 characters on the 4x40 displays are accessed with 2 controllers. The first controller handles the top two lines; the second controller is conected to the bottom two lines. They share all I/O lines except the "E". Logically, the display is like two displays connected to the MPU as the "E" lines must be independent. Remember to turn off the cursor when moving from one half of the display to the other to avoid viewer distraction.

**4x16/20** - Because of the way the controller and drivers are connected to make maximum use of their outputs, special attention must be paid to the addresses of these displays. Logically, line 3 follows line 1, and line 4 follows line 2. When the cursor gets to the end of line 1, it will jump to line 3. Keeping track of cursor location for proper positioning is important.

|    | 4 X 10 |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

|----|--------|----|----|----|----|----|----|----|----|----|----|----|----|----|----|

| 80 | 81     | 82 | 83 | 84 | 85 | 86 | 87 | 88 | 89 | 8A | 8B | 8C | 8D | 8E | 8F |

| C0 | C1     | C2 | C3 | C4 | C5 | C6 | C7 | C8 | C9 | CA | СВ | CC | CD | CE | CF |

| 90 | 91     | 92 | 93 | 94 | 95 | 96 | 97 | 98 | 99 | 9A | 9B | 9C | 9D | 9E | 9F |

| D0 | D1     | D2 | D3 | D4 | D5 | D6 | D7 | D8 | D9 | DA | DB | DC | DD | DE | DF |

4 Line by 16 Character Addresses

|       | 4 X 20         |                                           |                                                    |                                                             |                                                                      |                                                                               |                                                                                        |                                                                                                 |                                                                                                          |                                                                            |                                                                                                                            |                                                                                                                                     |                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|-------|----------------|-------------------------------------------|----------------------------------------------------|-------------------------------------------------------------|----------------------------------------------------------------------|-------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 83 84 | 85 86          | 87                                        | 88                                                 | 89                                                          | 8A                                                                   | 8B                                                                            | 8C                                                                                     | 8D                                                                                              | 8E                                                                                                       | 8F                                                                         | 90                                                                                                                         | 91                                                                                                                                  | 92                                                                                                                                           | 93                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| C3 C4 | C5 C6          | C7                                        | C8                                                 | C9                                                          | CA                                                                   | СВ                                                                            | CC                                                                                     | CD                                                                                              | CE                                                                                                       | CF                                                                         | D0                                                                                                                         | D1                                                                                                                                  | D2                                                                                                                                           | D3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 97 98 | 99 9A          | 9B                                        | 9C                                                 | 9D                                                          | 9E                                                                   | 9F                                                                            | A0                                                                                     | A1                                                                                              | A2                                                                                                       | A3                                                                         | A4                                                                                                                         | A5                                                                                                                                  | A6                                                                                                                                           | A7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| D7 D8 | D9 DA          | DB                                        | DC                                                 | DD                                                          | DE                                                                   | DF                                                                            | E0                                                                                     | E1                                                                                              | E2                                                                                                       | E3                                                                         | E4                                                                                                                         | E5                                                                                                                                  | E6                                                                                                                                           | E7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|       | C3 C4<br>97 98 | C3 C4 C5 C6<br>97 98 99 9A<br>D7 D8 D9 DA | C3 C4 C5 C6 C7<br>97 98 99 9A 9B<br>D7 D8 D9 DA DB | C3 C4 C5 C6 C7 C8<br>97 98 99 9A 9B 9C<br>D7 D8 D9 DA DB DC | C3 C4 C5 C6 C7 C8 C9<br>97 98 99 9A 9B 9C 9D<br>D7 D8 D9 DA DB DC DD | C3 C4 C5 C6 C7 C8 C9 CA<br>97 98 99 9A 9B 9C 9D 9E<br>D7 D8 D9 DA DB DC DD DE | C3 C4 C5 C6 C7 C8 C9 CA CB<br>97 98 99 9A 9B 9C 9D 9E 9F<br>D7 D8 D9 DA DB DC DD DE DF | C3 C4 C5 C6 C7 C8 C9 CA CB CC<br>97 98 99 9A 9B 9C 9D 9E 9F A0<br>D7 D8 D9 DA DB DC DD DE DF E0 | C3 C4 C5 C6 C7 C8 C9 CA CB CC CD<br>97 98 99 9A 9B 9C 9D 9E 9F A0 A1<br>D7 D8 D9 DA DB DC DD DE DF E0 E1 | C3 C4 C5 C6 C7 C8 C9 CA CB CC CD CE<br>97 98 99 9A 9B 9C 9D 9E 9F A0 A1 A2 | C3 C4 C5 C6 C7 C8 C9 CA CB CC CD CE CF<br>97 98 99 9A 9B 9C 9D 9E 9F A0 A1 A2 A3<br>D7 D8 D9 DA DB DC DD DE DF E0 E1 E2 E3 | C3 C4 C5 C6 C7 C8 C9 CA CB CC CD CE CF D0<br>97 98 99 9A 9B 9C 9D 9E 9F A0 A1 A2 A3 A4<br>D7 D8 D9 DA DB DC DD DE DF E0 E1 E2 E3 E4 | C3 C4 C5 C6 C7 C8 C9 CA CB CC CD CE CF D0 D1<br>97 98 99 9A 9B 9C 9D 9E 9F A0 A1 A2 A3 A4 A5<br>D7 D8 D9 DA DB DC DD DE DF E0 E1 E2 E3 E4 E5 | 83       84       85       86       87       88       89       8A       8B       8C       8D       8E       8F       90       91       92         C3       C4       C5       C6       C7       C8       C9       CA       CB       CC       CD       CE       CF       D0       D1       D2         97       98       99       9A       9B       9C       9D       9E       9F       A0       A1       A2       A3       A4       A5       A6         D7       D8       D9       DA       DB       DC       DD       DE       DF       E0       E1       E2       E3       E4       E5       E6 |

#### 4 Line by 20 Character Addresses

Line1 80 81 82 83 84 85 86 87 88 89 8A 8B 8C 8D 8E 8F 90 91 92 93 94 95 96 97 ... A5 A6 A7 Line2 C0 C1 C2 C3 C4 C5 C6 C7 C8 C9 CA CB CC CD CE CF D0 D1 D2 D3 D4 D5 D6 D7 ... E5 E6 E7 Line3 80 81 82 83 84 85 86 87 88 89 8A 8B 8C 8D 8E 8F 90 91 92 93 94 95 96 97 ... A5 A6 A7 Line4 C0 C1 C2 C3 C4 C5 C6 C7 C8 C9 CA CB CC CD CE CF D0 D1 D2 D3 D4 D5 D6 D7 ... E5 E6 E7

#### 4 Line by 40 Character Addresses

| Complete RAM Addresses                          |                                           |  |  |  |  |  |  |  |  |  |

|-------------------------------------------------|-------------------------------------------|--|--|--|--|--|--|--|--|--|

| 1 x 40                                          |                                           |  |  |  |  |  |  |  |  |  |

| 1 x 24                                          |                                           |  |  |  |  |  |  |  |  |  |

| 1 x 20                                          |                                           |  |  |  |  |  |  |  |  |  |

| 1 x 16                                          |                                           |  |  |  |  |  |  |  |  |  |

| 1 x 8                                           |                                           |  |  |  |  |  |  |  |  |  |

| 80 81 82 83 84 85 86 87 88 89 8A 8B 8C 8D 8E 8F | 90 91 92 93 94 95 96 97 A5 A6 A7 C5 C6 C7 |  |  |  |  |  |  |  |  |  |

1 Line Display Addresses

2 Line Display Addresses

### F. INSTRUCTION TABLE

| Instruction                  | RS | R/W | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 | Description                                                                                                                                 | Execution<br>Time<br>(when F <sub>cp</sub> or<br>f <sub>osc</sub> is 250KHz) |

|------------------------------|----|-----|-----|-----|-----|-----|-----|-----|-----|-----|---------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|

| Clear Display                | 0  | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 1   | Clears Display and<br>returns cursor to the<br>Home Position<br>(Address 00)                                                                | 80uS =<br>1.64mS                                                             |

| Return Home                  | 0  | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 1   | *   | Returns cursor to<br>Home Position.<br>Returns shifted<br>display to original<br>position. Does not<br>clear display                        | 40uS = 1.6mS                                                                 |

| Entry Mode Set               | 0  | 0   | 0   | 0   | 0   | 0   | 0   | 1   | I/D | s   | Sets DD RAM<br>counter to<br>increment or<br>decrement (I/D)<br>Specifies cursor or<br>display shift during<br>to Data Read or<br>Write (S) | 40uS                                                                         |

| Display<br>ON/OFF<br>Control | 0  | 0   | 0   | 0   | 0   | 0   | 1   | D   | с   | В   | Sets Display<br>ON/OFF (D), cursor<br>ON/OFF (C), and<br>blink character at<br>cursor position                                              | 40uS                                                                         |

| Cursor or<br>Display Shift   | 0  | 0   | 0   | 0   | 0   | 1   | S/C | R/L | *   | *   | Moves cursor or<br>shifts the display<br>w/o changing DD<br>RAM contents                                                                    | 40uS                                                                         |

|                              |    |     |     |     |     |     |     |     |     |     | Sets data bus                                                                                                                               |                                                                              |

| Function Set                                                                                                                                                                                                                                   | 0                             | 0               | 0  | 0 1 DL N F * *                                                                                                                                                                                                                                                          | iengtn (חב), # or<br>display lines (N),<br>and character font<br>(F)                                                                                                                                                                                      | 40uS                                                                                                                                                               |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|-----------------|----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Set CG RAM<br>Address                                                                                                                                                                                                                          | 0                             | 0               | 0  | 1 A <sub>CG</sub>                                                                                                                                                                                                                                                       | Sets CG RAM<br>address. CG RAM<br>data is sent and<br>received after this<br>instruction                                                                                                                                                                  | 40uS                                                                                                                                                               |

| Set DD RAM<br>Address                                                                                                                                                                                                                          | 0                             | 0               | 1  | A <sub>DD</sub>                                                                                                                                                                                                                                                         | Sets DD RAM<br>address. DD RAM<br>data is sent and<br>received after this<br>instruction                                                                                                                                                                  | 40uS                                                                                                                                                               |

| Read Busy Flag<br>& Address                                                                                                                                                                                                                    | 0                             | 1               | BF | AC                                                                                                                                                                                                                                                                      | Reads Busy Flag<br>(BF) and address<br>counter contents                                                                                                                                                                                                   | 1uS                                                                                                                                                                |

| SIZE=2>Write<br>Data from DD<br>or CG RAM                                                                                                                                                                                                      | 1                             | 0               |    | Write Data                                                                                                                                                                                                                                                              | Writes data to DD<br>or CG RAM and<br>increments or<br>decrements<br>address counter<br>(AC)                                                                                                                                                              | 40uS                                                                                                                                                               |

| Read Data from<br>DD or CG RAM                                                                                                                                                                                                                 | 1                             | 1               |    | Read Data                                                                                                                                                                                                                                                               | Reads data from<br>DD or CG RAM and<br>increments or<br>decrements<br>address counter<br>(AC)                                                                                                                                                             | 40uS                                                                                                                                                               |

| I/D=1: Incremen<br>S=1: Display Sh<br>entry<br>S/C=1: Display S<br>unchanged)<br>R/L=1: Shift to th<br>DL=1: 8 bits<br>N=1: 2 Lines<br>F=1: 5x10 Dot F<br>D=1: Display ON<br>C=1: Cursor ON<br>B=1: Blink ON<br>BF=1: Cannot ac<br>instruction | ift o<br>Shift<br>ne F<br>ont | t (RAI<br>Right |    | I/D=0: Decrements<br>S=0: Cursor Shift on data entry<br>S/C=0: Cursor Shift (RAM<br>unchanged)<br>R/L=0: Shift to the Left<br>DL=0: 4 bits<br>N=0: 1 Line<br>F=0: 5x7 Dot Font<br>D=0: Display OFF<br>C=0: Cursor OFF<br>B=0: Blink OFF<br>BF=0: Can accept instruction | Definitions:<br>DD RAM: Display<br>data RAM<br>CG RAM:<br>Character generator<br>RAM<br>A <sub>CG</sub> : CG RAM<br>Address<br>A <sub>DD</sub> : DD RAM<br>Address(Cursor<br>Address)<br>AC: Address<br>Counter used for<br>both DD and CG<br>RAM Address | Execution<br>Time changes<br>when<br>Frequency<br>changes per<br>the following<br>example:<br>If $F_{CP}$ or $f_{osc}$ is<br>27 KHz<br>40uS x<br>250/270 =<br>37uS |

## **G. INSTRUCTION DESCRIPTION**

#### CLEAR DISPLAY

#### CODE

| RS | R/W | DB7 |        | DB0 |

|----|-----|-----|--------|-----|

| 0  | 0   | 0   | 000000 | 1   |

Writes space code "20" (hexadecimal) into all the DD RAM addresses. The cursor returns to Address 0 (ADD="80") and display, if it has been shifted, returns to the original position. In other words, display disappears and the cursor goes to the left edge of the display (the first line if a 2 or 4 line display module is used).

#### **RETURN HOME**

| COI  | DE     |     |       |     |

|------|--------|-----|-------|-----|

| RS   | R/W    | DB7 |       | DB0 |

| 0    | 0      | 0   | 00001 | *   |

| * Do | n't Ca | are |       |     |

Returns the cursor to Address 0 (ADD="80") and display, if it has been shifted, to the original position. The DD RAM contents remain unchanged.

#### ENTRY MODE SET

CODE

| RS | R/W | DB7 |          | DB0 |

|----|-----|-----|----------|-----|

| 0  | 0   | 0   | 00001I/D | S   |

I/D: Increments (I/D=1) or decrements (I/D=0) the DD RAM address by one when writing or reading a character code from DD RAM. The cursor moves to the right when incremented by one. The same applies to writing and reading CG RAM.

S: Shifts the entire display to either the right or the left when S is 1; to the left when I/D=1 and to the right when I/D=0. Therefore, the cursor looks as if stood stil while only the display has moved. Display is not shifted when reading from DD RAM. Display is not shifted when S=0.

#### **DISPLAY ON/OFF CONTROL**

CODE

| RS | R/W | DB7 |        | DB0 |

|----|-----|-----|--------|-----|

| 0  | 0   | 0   | 0001DC | В   |

**D**: Display is turned ON when D=1 and OFF when D=0. When display is turned off due to D=0, the display data remains in the DD RAM and it can be displayed immediately by setting D=1.

**C**: The cursor is displayed when C=1 and not displayed when C=0. Even if the cursor disappears, function of I/D, etc. does not change during display data write. The cursor is displayed using 5 dots in the 8th lines when the  $5 \times 7$  dot character font is selected and in the 11th line when  $5 \times 10$  dot character font is selected.

**B**: The character residing at the cursor position blinks when B=1. The blink is done by switching between all dots ON and display characters at 0.4 second interval. The cursor and the blink can be set concurrently.

Detached Atta Cursor Position

Attached

**Blinking Character**

#### **CURSOR OR DISPLAY SHIFT**

CODE

| <u> </u> |        |      |   |     |     |     |   |     |

|----------|--------|------|---|-----|-----|-----|---|-----|

| RS       | S R/V  | V DB | 7 |     |     |     |   | DB0 |

| 0        | 0      | 0    | 0 | 0 1 | S/C | R/L | * | *   |

| * D      | on't C | Care |   |     |     |     |   |     |

Shifts the cursor position or display to the right or left without writing or reading the display data. This function is used for correction or search of display. S/C R/L

0 0 Shifts the cursor position to the left. (AC is decremented by one.)

- 0 1 Shifts the cursor position to the right. (AC is incremented by one).

- 1 0 Shifts the entire display to the left. The cursor follows the display shift.

- 1 1 Shifts the entire display to the right. The cursor follows the display shift.

#### FUNCTION SET

CODE

| RS   | R/W   | DB7 |   |    |    |     | DB0 |

|------|-------|-----|---|----|----|-----|-----|

| 0    | 0     | 0   | 0 | DL | NF | = * | *   |

| * Do | n't C | are |   |    |    |     |     |

\* Don't Care

**DL:** Sets interface data length. Data is sent or received in 8 bit length (DB7-DB0) when DL=1 and 4 bit length (DB7-DB4) when DL=0. When 4 bit length is selected, data must be sent or received in 2 operations.

N: Sets number of display lines.F: Sets character font.(Together, N & F set the duty cycle).

#### SET CG RAM ADDRESS

CODE

| 001 |     |     |   |    |   |   |   |     |

|-----|-----|-----|---|----|---|---|---|-----|

| RS  | R/W | DB7 |   |    |   |   |   | DB0 |

| 0   | 0   | 0   | 1 | AA | A | A | A | A   |

Sets the CG RAM address in a binary number of AAAAAA to the address counter, and data is written or read from the MPU related to the CG RAM after this. This is used for programming the Character Generator (CG) RAM.

#### SET DD RAM ADDRESS

| CODE  |       |        |     |

|-------|-------|--------|-----|

| RS R/ | W DB7 |        | DB0 |

| 0 0   | 1     | AAAAAA | А   |

Sets the DD RAM address in a binary number of AAAAAAA in the address counter. Data is written or read from the MPU related to the DD RAM after this. When N=0 (1 line display), AAAAAAA is "00" to "47" (hexadecimal) When N=1 (2 line display),

AAAAAAA for the first line is "00" to "27" and "40" to "67", (hexadecimal) for the second line. Because the MSB is set to "!", the hex codes are actually "80" to "C0", "80" to "A7", and "C0" to "E7" respectively. See Display Addressing for more information.

#### READ BUSY FLAG AND ADDRESS

CODE

| RS | R/W | DB7 |        | DB0 |

|----|-----|-----|--------|-----|

| 0  | 1   | BF  | AAAAAA | A   |

When BF=1, the system is internally operating on a previously received instruction. The next instruction will not be received until BF=0. The value of the address counter also to read during this operation, and is given in binary AAAAAAA. Whether CG or DD RAM address is read is determined by the previous instruction.

#### WRITE DATA TO CG OR DD RAM

| CODE   |     |        |    |

|--------|-----|--------|----|

| RS R/W | DB7 | DE     | 30 |

| 1 0    | D   | DDDDDD |    |

Writes binary 8 bit data DDDDDDD to the CG or the DD RAM. Whether the CG or the DD RAM is to be written is determined by the previous designation (CG RAM address setting or DD RAM address setting). After write, the address is automatically incremented or decremented by one according to entry mode. Display shift also follows the entry mode.

#### **READ DATA FROM CG OR DD RAM**

CODE

| 0000   |     |       |     |

|--------|-----|-------|-----|

| RS R/W | DB7 |       | DB0 |

| 1 1    | D   | DDDDD | D   |

Reads binary 8 bit data DDDDDDD from the CG or the DD RAM. Whether the CG RAM or the DD RAM is to be read is determied by the previous designation. Prior to inputting this read instruction, either the CG RAM address set instruction or the DD RAM address set instruction must be executed. If it is not done, the first read data becomes invalid, and data of the next address is read normally from the second read. After read, the address is automatically incremented or decremented by one according to the entry mode. However, display shift is not performed regardless of entry mode types.

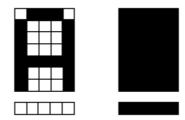

### H. THE USE OF CG-RAM

Character Generator (CG) RAM is a useful accessory. It does not have to be used or attended to during any normal display operation. CG RAM allows the creation of up to 8 special character or symbols. Once programmed, the newly formed characters may be accessed as if they were in the "normal" CG ROM. This ROM contains 192 unchangeable characters. Thus the CG RAM expands the character representation available to the user.

NOTE: This is a RAM, and must be reprogrammed if display power is interrupted. If used regularly, programming can be made part of the initialization routine.

There are two distinct areas of RAM within the display module. The main area, 80 bytes wide, is dedicated to the display and is called Display Data (DD) RAM. CG RAM consists of 64 bytes which range from 40 to 7F (hex), or 4 5x10 (or 5x11) symbols. 40-47 locate the first, custom 5x7 character. 40 is the top row of this character, 47 is the 8th row. Similarly, 48-4F locate the second CG character, and 78-7F locate the 8th custom character. The locations 40-7F are the CG "Programming" locations only! Once programmed, these special characters are displayed by writing to character font locations 00-07 (hex). 00 will return that character residing in locations 40-47, 01 returns 48-4F. etc. (See Font Chart).

While the CG RAM byte is 8 bits wide, only the 5 least significant bits appear on the LCD. Thus D4 represents the left-most dot and D0 the right-most dot. To illustrate, loading a CG RAM byte with 1F turns all dots in that row on; loading a byte with 00 turns all dots off. All 7 or 8 rows must be programmed at each desired CG location.

Programming procedure is:

a) with RS=0 enter the address of the top row of the character to be programmed (i.e. 40,48,50, etc.) b) with RS=1 enter pattern data for row 1 (top row)

c) continue to enter pattern data for rows 2-8; it is not necesary to enter additional addresses if the module has been initialized with command 06 (auto increment of cursor).

This procedure may be continued until all CG bytes have been loaded.

The CG RAM can create an attractivew, "reverse-video"  $3 \times 5$  pattern. Numerals look especially good in this format. Most letters can be executed. The limitation of 8 characters can be circumvented by creating a "library" of custom symbols, each totalling 8, resident in the host system. Eight custom symbols can be displayed at any ONE time. The CG RAM can be periodically reloaded as display requirements change. If you reload a CG location which is currently on the display, the change will be immediately apparent. Displays employing multiple controllers (ie.  $4 \times 40$ ,  $2 \times 80$ .  $4 \times 80$ ) may create 8 symbols per controller. The CG RAM adds interest and flexibility to the LCD module.

| CG RAM, DD RAM, and pattern examples for 5 x 7 Dot Character patterns | CG RAM, DD RAM, and | pattern examples | s for 5 x 7 Dot | Character patterns |

|-----------------------------------------------------------------------|---------------------|------------------|-----------------|--------------------|

|-----------------------------------------------------------------------|---------------------|------------------|-----------------|--------------------|

| Character Codes<br>(DD RAM Data) | CG RAM Address      | Character Patterns<br>(CG RAM Data)         |

|----------------------------------|---------------------|---------------------------------------------|

| 76543210                         | 543210              | 76543210                                    |

|                                  |                     | < <higher bits<="" order="" td=""></higher> |

| Lower order bits >>              | Lower order bits >> | Lower order bits >>                         |

|                                  | 000000              | * * * 1 1 1 1 0                             |

|                                  | 000001              | * * * 1 0 0 0 1                             |

|                                  | 000010              | * * * 1 0 0 0 1 - Character                 |

| 0000*000                         | 000011              | * * * 1 1 1 1 0 - Pattern                   |

|                                  | 000100              | * * * 1 0 1 0 0 - Example (1)               |

|                                  | 000101              | * * * 1 0 0 1 0                             |

|                                  | 000110              | * * * 1 0 0 0 1                             |

|                                  | 000111              | * * * 0 0 0 0 0 - Cursor Position           |

|                                  | 001000              | * * * 1 0 0 0 1                             |

|                                  | 001001              | * * * 0 1 0 1 0                             |

|                                  | 001010              | * * * 1 1 1 1 1 - Character                 |

| 0000*001                         | 001011              | * * * 0 0 1 0 0 - Pattern                   |

|                                  | 001100              | * * * 1 1 1 1 1 - Example (2)               |

|                                  | 001101              | * * * 0 0 1 0 0                             |

|                                  | 001110              | * * * 0 0 1 0 0                             |

|                                  | 001111              | * * * 0 0 0 0 0 - Cursor position           |

| 0.0.0.*0.1.0                     | 010000              | * * * 1 0 0 0 1                             |

| 0000*010                         | 010001              | * * * 1 1 0 1 1                             |

|                                  | 111101              | * * * 0 0 1 0 0 - Character Pattern         |

| 0000*111                         | 11110               | * * * 0 1 0 1 0 - Example (8)               |

|                                  | 1 1 1 1 1 1         | * * * 1 1 0 1 1 - Cursor position           |

#### \*Don't Care

Notes:

- 1. Character code bits 0-2 correspond to CG RAM address bits 3-5 for a total of 8 patterns.

- 2. CG RAM address codes 0-2 designate character pattern line. The 8th line is the cursor position. It is logically "OR'ed" with the cursor instruction.

- 3. Character patterns are loaded into CG RAM data bits 0-4 as shown in the table. (Bit 4 is the left side). Since CG RAM bits 5-7 are not used, they may be used for general data RAM.

- CG RAM patterns are displayed on the LCD when character code bits 4-7 are all "0". Bit 3 is a don't care bit. Therefore, character pattern (1) can be selected with character code "00" or "08" (hexadecimal).

- 5. "1" in the character pattern turn a dot "ON". "0" indicates a non-selected dot.

#### CG RAM, DD RAM, and pattern examples for 5 x 10 Dot Character patterns

| Character Codes<br>(DD RAM Data) | CG RAM Address      | Character Patterns<br>(CG RAM Data)         |

|----------------------------------|---------------------|---------------------------------------------|

| 76543210                         | 543210              | 76543210                                    |

|                                  |                     | < <higher bits<="" order="" td=""></higher> |

| Lower order bits >>              | Lower order bits >> | Lower order bits >>                         |

|                                  | 000000              | * * * 0 0 0 0 0                             |

|                                  | 000001              | * * * 0 0 0 0 0                             |

|                                  | 000010              | * * * 1 0 1 1 0                             |

|                                  | 000011              | * * * 1 1 0 0 1 - Character                 |

|                                  | 000100              | * * * 1 0 0 0 1 - Pattern                   |

|                                  | 000101              | * * * 1 0 0 0 1 - Example (1)               |

|                                  | 000110              | * * * 1 1 1 1 0                             |

| 0000*00*                         | 000111              | * * * 1 0 0 0 0                             |

|                                  | 001000              | * * * 1 0 0 0 0                             |

|                                  | 001001              | * * * 1 0 0 0 0                             |

|                                  | 001010              | * * * 0 0 0 0 0 - Cursor Position           |

|                                  | 001011              | * * * * * * *                               |

|                                  | 001100              | * * * * * * *                               |

|                                  | 001101              | * * * * * * *                               |

|                                  | 001110              | * * * * * * *                               |

|                                  | 001111              | * * * * * * *                               |

| 0 0 0 0 * 0 1 *                  | 010000              | * 0 1 0 0 0 0 *                             |

| 0000*01*                         | 010001              | * 0 1 0 0 0 1 *                             |

|                                  | 111101              | * * * * * * * * - Character                 |

| 0000*11*                         | 111110              | * * * * * * * * - Pattern                   |

|                                  | 11111               | * * * * * * * * - Example (4)               |

#### \*Don't Care

#### Notes:

- 1. Character code bits 1 & 2 correspond to CG RAM address bits 4 & 5 for a total of 4 patterns.

- CG RAM address codes 0-3 designate character pattern line. The 11th line is the cursor position. It

is logically "OR'd" with the cursor instruction. Since lines 12-16 are not used for the display, they

may be used as general data RAM.

- 3. Character patterns are loaded into CG RAM data bits 0-4 as shown in the table. (Bit 4 is the left side). Since CG RAM bits 5-7 are not used, they may be used for general data RAM.

- CG RAM patterns are displayed on the LCD when character code bits 4-7 are all "0". Bits 0 & 3 are a "don't care" bits. Therefore, character pattern (1) can be selected with character code "00". "01", "08", or "09" (hexadecimal).

- 5. "1" in the character pattern turn a dot "ON". "0" indicates a non-selected dot.

## **IV APPENDIX**

### A. DESIGNER'S CHECKLIST

Below is a summary of hardware design considerations and precautions:

#### POWER:

- 1. Supply a transient-free +5V- this supply should power all components which drive the data control bus.

- 2. Provide the specified "VDD-VO" voltage to the module's contrast pin (VO). Do not connect a capacitor between this point and ground, VO must never exceed VDD.

- 3. This VDD-VO spec may exceed 5V, on some models, indicating that a negative supply is required. The negative source is connected to one end of the VO control potentiometer.

- 4. Never insert or remove a module from a live circuit.

#### HARDWARE:

- 1. Develop a uniquely decoded "E" strobe puse, active high, to accompany each module transaction.

- 2. This "E" strobe must be at least 450 nS wide.

- 3. Module inputs RS and R/W "set-up" 140 nS prior to the rise of "E".

- 4. Data sets up 195 nS prior to the fall of "E".

- 5. RS, R/W, and data all "hold" 10 nS after the fall of "E".

- 6. Assign the display a "global" address which generates a uniquely decoded output.

- 7. Assign 1 or 2 additional bits, whether address or control, to drive the RS and R/W inputs. (R/W may be grounded for write-only applications.

- 8. Observe the module's "execution-time". (See software section). The module "goes-busy" for some 40 to 1600 microseconds after a transaction. Transfers during this "busy" period will not be accepted.

- 9. Utilize the host's extended timing mode, if available, when transacting with the LCD. Use those instructions which prolong the RD and WR, or other appropriate data strobes.

- 10. If a parallel port is used to drive the RS, R/W and "E" control lines, be certain not to set the "E" control lines, be certain not to set the "E" bit simultaneously with RS and R/W. This violates the moduel's set-up time. A separate instruction must be employed.

#### MOUNTING

- 1. Install so that the module is warp free and no pressure is applied to the bezel.

- 2. Protect the display surface from contamination and foreign objects.

### **B. PRECAUTIONS IN HANDLING AND OPERATING LCD MODULES**

These precautions apply equally to modules from all makers - not just Densitron. When these rules are followed an extraordinary service life can be achieved. Violation of these guidelines can cause problems ranging from erratic operation to catastrophic display failure.

#### POWER SUPPLY PRECAUTIONS:

- 1. Identify and, at all times, observe absolute maximum ratings for both logic and LC driver. Note that there is some variance between models. Check yours!

- 2. Prevent the application of reverse polarity, however, briefly.

- 3. Use a clean power source free from transients. Power up conditions are occasionally "jolting".

- 4. The +5V power for the module should also supply the power to all devices which may access the display. Don't allow the data bus to be driven when the logic supply is disabled.

- 5. Do NOT install a capacitor between the VO (contrast) pin and ground. VDD must, at all times, exceed the VO voltage level. The capacitor combines with the contrast potentiometer to form an R-C network which "holds-up" VO, at the power-down, damaging the module.

#### **OPERATING PRECAUTIONS:**

- 1. Do NOT plug or unplug the module which the system is live.

- 2. Minimize the cable run between the module and host. Long lengths may introduce noise or damaging voltages due to antenna-effect.

- 3. Don't disable the EL backlight by interrupting the AC line. Unloaded inverters produce voltage extremes which may arc within a cable or at the display.

#### MECHANICAL/ENVIRONMENTAL PRECAUTIONS:

- 1. Improper soldering is the major cause of module difficulty, Water based solders are not recommended. Densitron recommends Kester"44" resin solder. The flux is non-corrosive and electrically non-conductive. The flux residues do not need to be cleaned off.

- 2. Mount the module so that it is free from torque and physical loads.

- 3. The display font is an easily scratched, plastic polarizer. Avoid contact and clean only when necessary with soft, absorbent cotton dampened with petroleum benzine.

- 4. Employ anti-static procedures, always, while handling the module. Use a lear protection plate between the module and the outside world.

- 5. Prevent moisture build-up upon the module.

### C. TROUBLESHOOTING GUIDE

#### Sympton:

A) No display after initialization and data sent. Probable cause:

- 1. VO voltage not properly set. Check specification. Some displays require a negative voltage at this pin. Set up VO with potentiometer that will adjust over full range from VDD to VSS, or VDD to VEE (-5VDC). (See Power Supply Section).

- 2. Timing violated. Check that all set up times are followed. check that Enable pulse must be 450nS minimum.

- 3. Execution times violated. Do not send signals for 15mS after power up. Allow 1.6mS after Clear and Return Home Instructions are sent; 40mS after other instructions and the data are sent.

- 4. Improper initialization. It's always a good idea to send an initialization routine after power up. The internal routine leaves the display in the OFF condition.

- 5. Do not store in direct sunlight.

- 6. If leakage of the liquid crystal material should occur, all contact with this material, particularly ingestion, must be avoided. If skin or clothing becomes contaminated, wash thoroughly with soap and water.

- 7. Display misconnected. Check all connections. Ensure no I/O pads are bridged.

- 8. Signal levels incorrect. Insure data bus components have CMOS or TTL level outputs. Measure 2.4VDC min. for logic high and I/O connections on display.

- 9. Power supply out of tolerance or "dirty". Check +5VDC and ground.

B) Displays randomly or unreliably. Probable cause: Check b), c). d), e), & g) above.

C) Only 1 line will display on a 2 line module.Probable cause:Display initialized as 1 line display. Send proper initialization codes.

C) Missing rows or columns of dots

Probable cause:

Display has been mounted so that torque or pressure is applied to PPC and/or bexel. Unmount and recheck.

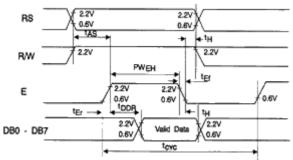

### D. TIMING DIAGRAMS

Write Operation

| ITEM                  | SYM      | MIN  | MAX | UNIT |

|-----------------------|----------|------|-----|------|

| Enable Cycle Time     | tcycE    | 1000 |     | nS   |

| Enable Pulse Width    | PW EH    | 450  |     | nS   |

| Enable Rise/Fall Time | tEr, tEf |      | 25  | nS   |

| Address Set-up Time   | tAS      | 140  |     | nS   |

| Address Hold Time     | tAH      | 10   |     | nS   |

| Data Start-up Time    | tDSW     | 195  |     | nS   |

| Data Hold Time        | tDHR     | 10   |     | nS   |

**Read Operation**

| ITEM                  | SYM      | MIN  | MAX | UNIT |

|-----------------------|----------|------|-----|------|

| Enable Cycle Time     | tcyc E   | 1000 |     | nS   |

| Enable Pulse Width    | PW E     | 450  |     | nS   |

| Enable Rise/Fall Time | tEr, tEf |      | 25  | nS   |

| Address Set-up Time   | tAS      | 140  |     | nS   |

| Address Hold Time     | tAH      | 10   |     | nS   |

| Data Delay Time       | tDSW     |      | 320 | nS   |

| Data Hold Time        | tDHR     | 10   |     | nS   |

### E. FONT CHART

|               | Upper          | 0                | 2      | 3     | 4  | 5        | 6       | 7           | A            | В         | С       | Ď    | E           | F    |

|---------------|----------------|------------------|--------|-------|----|----------|---------|-------------|--------------|-----------|---------|------|-------------|------|

| Lowe<br>4-bit | Upper<br>4-bit | 0000             | 0010   | 0011  |    | 0101     | 0110    | 0111        | 1010         | 1011      | 1100    | 1101 | 1110        | 1111 |

| 0             | xxxx0000       | CG<br>RAM<br>(1) |        | Ø     |    |          | ••      | <b>p</b>    |              |           | 5       |      | X           | p    |

| 1             | xxxxx0001      | (2)              | 1      | 1     | P  | 0        | .::     | q           |              | 7         | Щ.      | Ċ.,  |             | q    |

| 2             | xxxxx0010      | (3)              | ::     | 2     | 8  | R        | Ŀ       | ŀ           | T            | ·1        | ų       | :::  | ß           | 0    |

| 3             | xxxxx0011      | (4)              | #      | 3     | 0  | <u> </u> | €.      | <u></u>     | .1           | ņ         | Ť       | Ŧ    | 8           | ¢?   |

| 4             | xxxx0100       | (5)              | \$     | 4     | D  | T        |         | t.          | ŀ.           | 1         | ŀ       | 17   | <u> </u> .4 | Ω    |

| 5             | xxxxx0101      | (6)              | ".<br> |       |    |          | <u></u> | 1.4         | ::           | 7         |         |      | ß           | ü    |

| 6             | xxxxx0110      | Ø                | 8      | ÷     |    | Ų        | ÷       | Ņ           |              | ņ         |         |      | p           | 2    |

| 7             | xxxx0111       | (8)              |        | 7     | 0  | Ņ        | -       | l, l        | 7            | :         |         | ÷    | 9           | π    |

| 8             | xxxx1000       | (1)              | ÷.     | 8     |    | ×        | ŀ'n     | ×           | 4            | <u>_</u>  | <br>    | Ņ    | .,r         | X    |

| 9             | xxxx1001       | (2)              |        | 9     | 1  | P        | 1       | <u>ا</u> ي: | r <u>i</u> n | Ţ         |         | Iİ.  | ;           | Ч    |

| A             | xxxx1010       | (3)              | :‡:    |       |    |          | .1      | 2           |              |           | i `i    | Ŀ    |             | Ę.   |

| в             | xxxx1011       | (4)              |        | ;     | K  | Ľ        | k       | 4           | 7            | ţţ        | <u></u> |      | ×           | 3    |

| с             | xxxx1100       | (5)              | :      |       | I  | ÷        | 1       |             | 17           | :         | 7       | ņ    | ¢.          | P    |

| D             | xxxx1101       | (6)              | •••••  | ::::: | M  |          | m       | }           |              |           | •••     |      | ÷.          | ÷    |

| E             | xxxx1110       | Ø                |        | >     | ŀ- | ~`       | m       | ÷           | =            | 12        | : :     | ···  | ĥ           |      |

| F             | xxxx1111       | (8)              |        | ?     | 0  |          | $\Box$  | ÷           |              | <u>ار</u> |         | 8    | ö           |      |

### F. PROCESSOR SPECIFIC INTERFACE SUGGESTIONS

# G. DESCRIPTION OF POLARIZER TYPE for DENSITRON LIQUID CRYSTAL DISPLAYS

| ТҮРЕ                       | P/N<br>CODE | DESCRIPTION                                                   | DIRECT<br>SUNLIGHT                  | OFFICE<br>LIGHT              | SUBDUED<br>LIGHT       | VERY<br>LOW<br>LIGHT         | COMMENTS                                              |  |

|----------------------------|-------------|---------------------------------------------------------------|-------------------------------------|------------------------------|------------------------|------------------------------|-------------------------------------------------------|--|

| Reflective<br>Positive     | A           | Dark Characters<br>on a Light Gray or<br>Yellow<br>Background | Excellent                           | Very<br>Good                 | Poor                   | Unusable                     | Cannot be<br>backlit                                  |  |

| Transflective<br>Positive  | в           | Dark Characters<br>on a Light Gray or<br>Yellow<br>Background | Excellent<br>(Lamp Off)             | Very<br>Good<br>(Lamp<br>On) | Very Good<br>(Lamp On) | Very<br>Good<br>(Lamp<br>On) | Best Choice for all around use                        |  |

| Transmissive<br>Negative   | E           | Lighted<br>Characters on a<br>Dark Background                 | Poor (Lamp<br>On)                   | Good<br>(Lamp<br>On)         | Very Good<br>(Lamp On) | Excellent<br>(Lamp<br>On)    | Backlight must always be on                           |  |