## High-Speed Microcontroller User Guide

#### www.dalsemi.com

### **SECTION 1: INTRODUCTION**

The Dallas Semiconductor High-Speed Microcontroller is an 8051-compatible device that provides improved performance and power consumption compared to the original version. It retains instruction set and object code compatibility with the 8051, yet performs the same operations in fewer clock cycles. Consequently, more throughput is possible for the same crystal speed. As an alternative, the High-Speed Microcontroller can be run slowly to save power. The more efficient design allows a much slower crystal speed to get the same results as an original 8051, using much less power.

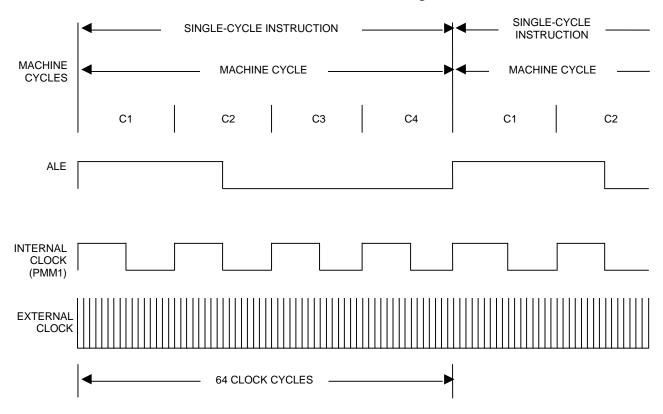

The fundamental innovation of the High-Speed Microcontroller is the use of only four clocks per instruction cycle compared with twelve for the original 8051. This results in up to 3 times improvement in performance. In addition, the High-Speed Microcontroller is updated with several new peripherals and features while providing all of the standard features of an 80C32. These include 256 bytes of on-chip RAM, 32 I/O ports, three 16-bit timer/counters, and an on-chip UART. All devices provide 256 bytes of RAM for variables and stack. 128 bytes can be reached using direct addressing and 128 using indirect addressing.

In addition to improved efficiency, members of the High-Speed Microcontroller family can operate at a maximum clock rate of 33 or 40 MHz. Combined with the 3 times performance, this allows for a maximum performance equivalent to a 99 or 120 MHz 8051. This level of computing power is comparable to many 16-bit processors, but without the added expense and complexity if implementing a 16-bit interface.

A number of peripherals were added to the original 80C32 core when designing the High-Speed Microcontroller family. Some devices have a programmable watchdog Timer to supervise the system. It will count up to a user programmable interval and then reset the CPU unless cleared by software. Other features such as a second, full-function UART and dual data pointers are available to minimize external interrupts allows greater flexibility in dealing with external events.

Some members of the High-Speed Microcontroller family incorporate Power Management Modes which allow the device to dynamically vary the internal clock speed from 4 clocks per cycle (default) to 64 or 1024 clocks per cycle. Because power consumption is directly proportional to clock speed, the device can reduce its operating frequency during periods of little or no activity. This greatly reduces power consumption. The switch-back feature allows the device to quickly return in divide by 4 mode upon receipt of an interrupt or serial port activity, allowing the device to respond to external events while in Power Management Mode.

Various memory configurations are available with the High-Speed Microcontroller family. EPROM and Mask programmable ROM versions are available for program memory. Some versions incorporate extended MOVX SRAM on-chip, reducing or eliminating the need for external data memory. This memory can be made nonvolatile in the DS87C530 through the use of an external lithium battery.

1 of 175 092299

### **SECTION 2: ORDERING INFORMATION**

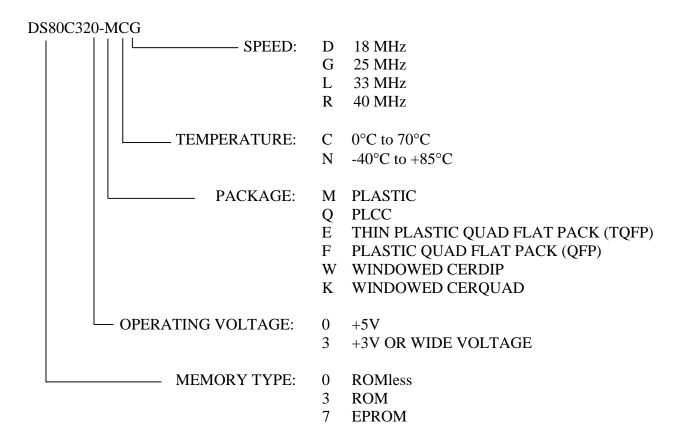

The High-Speed Microcontroller family follows the part numbering convention shown below. Note that all combinations of devices are not currently available. Please refer to individual data sheets for the available versions.

### **SECTION 3: ARCHITECTURE**

The High-Speed Microcontroller is based on the industry standard 80C52. The core is an accumulator based architecture using internal registers for data storage and peripheral control. It executes the standard 8051 instruction set. This section provides a brief description of each architecture feature. Details concerning the programming model, instruction set, and register description are provided in Section 4.

#### **ALU**

The ALU is responsible for math functions, comparisons, and general decision making in the High-Speed Microcontroller. The ALU is not explicitly used by software. Instruction decoding prepares the ALU automatically and passes it the appropriate data. The ALU primarily uses two special function registers (SFRs) as the source and destination for all operations. These are the Accumulator and B register. The ALU also provides status information in the Program Status Register. The SFRs are described below.

### SPECIAL FUNCTION REGISTERS

All peripherals and operations that are not explicit instructions in the High-Speed Microcontroller are controlled via Special Function Registers (SFRs). All SFRs are described in Section 4. The most commonly used registers that are basic to the architecture are also described below.

### **Accumulator**

The Accumulator is the primary register used in the High-Speed Microcontroller. It is the source and destination of most math, data movement, decisions, and other operations. Although it can be bypassed, most high-speed instructions require the use of the Accumulator (ACC) as one argument.

### **B** Register

The B register is used as the second 8-bit argument in multiply and divide operations. When not used for these purposes, the B register can be used as a general purpose register.

## **Program Status Word**

The Program Status Word holds a selection of bit flags that include the Carry Flag, Auxiliary Carry Flag, General Purpose Flag, Register Bank Select, Overflow Flag, and Parity Flag.

## Data Pointer(s)

The Data Pointer is used to designate a memory address for the MOVX instruction. This address can point to a MOVX RAM location, either on- or off-chip, or a memory mapped peripheral. When moving data from one memory area to another or from memory to a memory mapped peripheral, a pointer is needed for both the source and destination. Thus the High-Speed Microcontroller offers two data pointers. The user selects the active pointer via a dedicated SFR bit.

#### Stack Pointer

The microcontroller provides a Stack in the scratchpad RAM area discussed below. The Stack Pointer denotes the register location at the top of the Stack, which is the last used value. The user can place the Stack anywhere in scratchpad RAM by setting the Stack Pointer to that location.

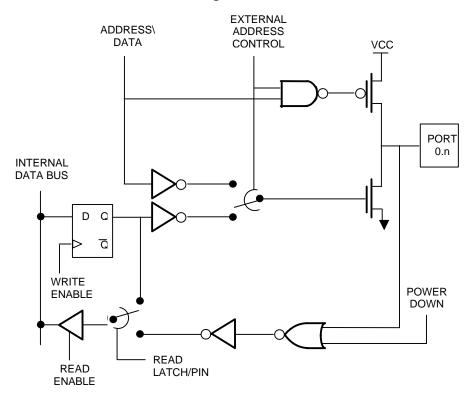

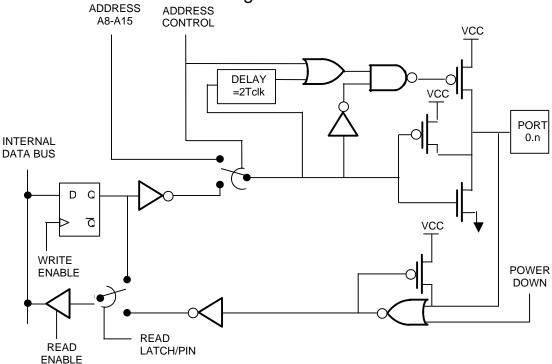

### I/O Ports

The standard High-Speed Microcontroller offers four 8-bit I/O ports. ROM less versions use Port 0 and Port 2 as address and data busses. In those versions, only two ports are available for general purpose I/O. Each I/O port is a Special Function Register that can be written or read. The I/O port has a latch that

retains the value which software writes. In general, during a read operation, software reads the state of the external pin. Each port is represented by a SFR location.

### **Timer/Counters**

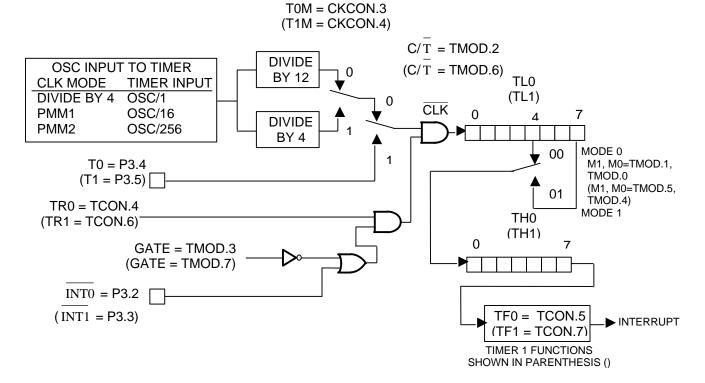

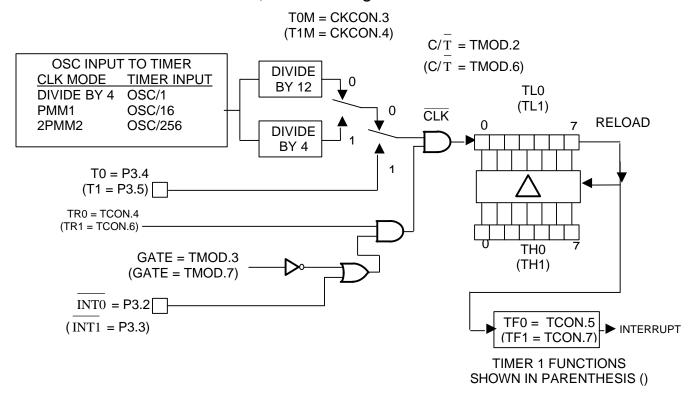

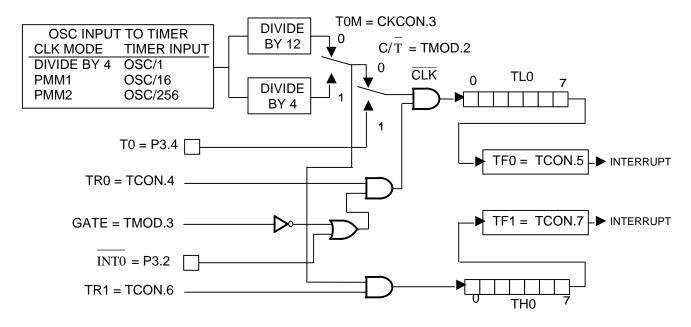

Three 16-bit Timer/Counters are available in the High-Speed Microcontroller. Each timer is contained in two SFR locations that can be written or read by software. The timers are controlled by other SFRs described in Section 4.

#### **UARTs**

The High-Speed Microcontroller provides one or two UARTs. These are controlled and accessed as SFRs. Each UART has an address that is used to read or write the UART. The same address is used for both read and write operations. The microcontroller distinguishes between a read and a write by the instruction. Each UART is controlled by its own SFR control register.

### SCRATCHPAD REGISTERS (RAM)

The High-Speed Core provides 256 bytes of Scratchpad RAM for general purpose data and variable storage. The first 128 bytes are directly available to software. The second 128 are available through indirect addressing discussed below. Selected portions of this RAM have other optional functions.

### Stack

The stack is a RAM area that the microcontroller uses to store return address information during Calls and Interrupts. The user can also place variables on the stack when necessary. The Stack Pointer mentioned above designates the RAM location that is the top of the stack. Thus, depending on the value of the Stack Pointer, the stack can be located anywhere in the 256 bytes of RAM. A common location would be in the upper 128 bytes of RAM, as these are accessible through indirect addressing only.

### **Working Registers**

The first thirty-two bytes of the Scratchpad RAM can be used as four banks of eight Working Registers for high speed data movement. Using four banks, software can quickly change context by simply changing to a different bank. In addition to the Accumulator, the Working Registers are commonly used as data source or destination. Some of the Working Registers can also be used as pointers to other RAM locations (indirect addressing).

### PROGRAM COUNTER

The Program Counter (PC) is a 16-bit value that designates the next program address to be fetched. Onchip hardware automatically increments the PC value to move to the next ROM location.

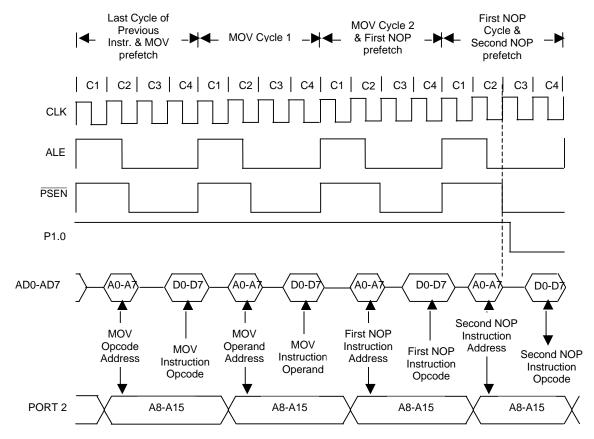

#### ADDRESS/DATA BUS

The High-Speed Microcontroller addresses a 64KB program and 64KB data memory area. In the ROMless versions, all memory is outside. Other versions use a combination of internal and external memory. When external memory is accessed, Ports 0 and 2 are used as a multiplexed address and data bus. Port 2 provides the address MSB. Even versions with internal memory can use the bus on Ports 0 and 2 to access more memory.

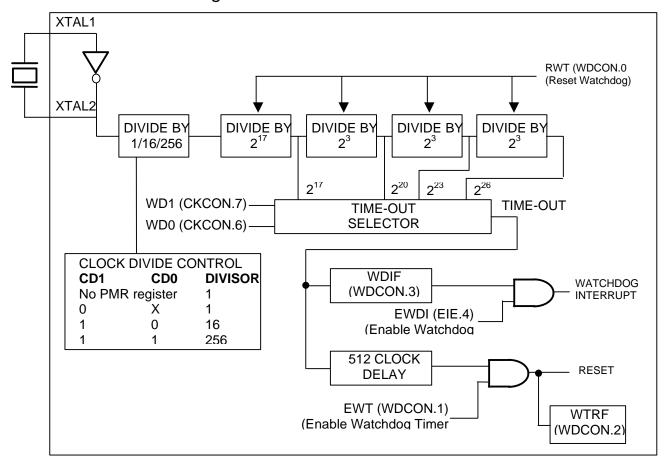

#### WATCHDOG TIMER

The Watchdog Timer provides a supervisory function for applications that cannot afford to run out of control. The Watchdog Timer is a programmable free running timer. If allowed to reach the termination of its count, if enabled, the Watchdog will reset the CPU. Software must prevent this by cleaning or resetting the Watchdog prior to its time-out.

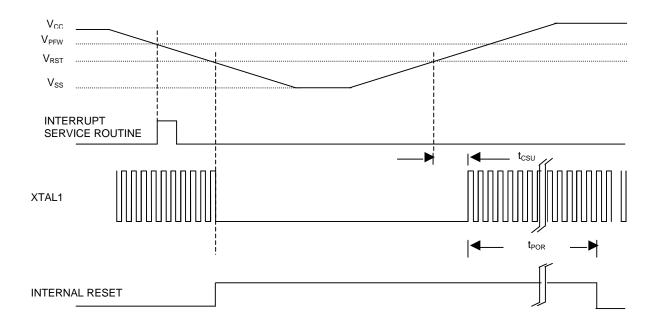

### POWER MONITOR

Some members of the High-Speed Microcontroller family incorporate a band-gap reference and analog circuitry to monitor the power supply conditions.  $V_{CC}$  begins to drop out of tolerance, the Power Monitor will issue an optional early warning Power-fail interrupt. If power continues to fall, the Power Monitor will invoke a reset condition. This will remain until power returns to normal operating voltage. The Power Monitor also functions on power-up, holding the microcontroller in a reset state until power is stable.

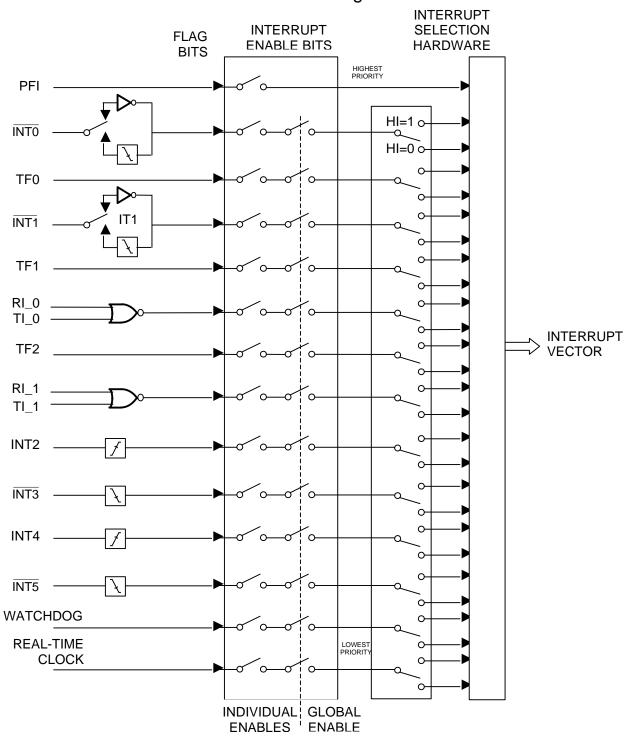

### **INTERRUPTS**

The High-Speed Microcontroller is capable of evaluating a number of interrupt sources simultaneously. Each version of the High-Speed Microcontroller provides a different number of interrupt sources. Each interrupt has an associated interrupt vector, flag, priority, and enable. These interrupts can be globally enabled or disabled.

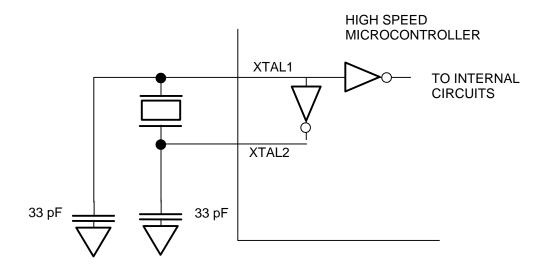

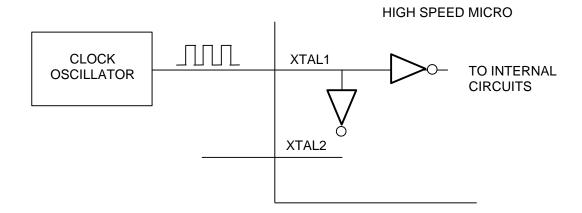

### TIMING CONTROL

The High-Speed Microcontroller provides an on-chip oscillator for use with an external crystal. This can be bypassed by injecting a clock source into the XTAL 1 pin. The clock source is used to create machine cycle timing (four clocks), ALE, PSEN, Watchdog, Timer, and serial baud rate timing. In addition, some devices incorporate an on-chip ring oscillator which can be used to provide an approximately 2-4 MHz clock source.

### REAL-TIME CLOCK

The DS87C530 incorporates a real-time clock (RTC), which is accessed via SFR locations. The RTC is divided into hour, minute, second, and subsecond registers, and also incorporates a 65536 day calendar. Alarm registers allow the RTC to issue interrupts at a specific time once a day, or as a recurring alarm every hour, minute or second. An external watch crystal and lithium power source allow the processor to maintain timekeeping in the absence of  $V_{\rm CC}$ .

### FEATURE SUMMARY

The High-Speed Microcontroller family offers a combination of features and peripherals as shown in Table 3-1. This User's Guide is designed as a comprehensive guide covering all features available in the High-Speed Microcontroller family. The designer should investigate the specific data sheet to determine which features are available on a particular device. Detailed information about newer members of the product family may be provided in separate documents until they can be assimilated into the High-Speed Microcontroller User's Guide.

## PRODUCT FEATURE MATRIX Table 3-1

| FEATURE                    | DS80C310  | DS80C320  | DS80C323  | DS83C520         | DS87C520      | DS87C530      | DS87C550                  |

|----------------------------|-----------|-----------|-----------|------------------|---------------|---------------|---------------------------|

| Internal Program ROM       |           |           |           | 16KB<br>Mask ROM | 16KB<br>EPROM | 16KB<br>EPROM | 8KB<br>EPROM              |

| Internal Scratchpad RAM    | 256 bytes | 256 bytes | 256 bytes | 256 bytes        | 256 bytes     | 256 bytes     | 256 bytes                 |

| Internal MOVX SRAM         |           |           |           |                  |               | 1KB SRAM      | 1KB SRAM                  |

| Serial Ports               | 1         | 2         | 2         | 2                | 2             | 2             | 2                         |

| External Interrupts        | 6         | 6         | 6         | 6                | 6             | 6             | 6                         |

| 16-bit Timers              | 3         | 3         | 3         | 3                | 3             | 3             | 3                         |

| Watchdog Timer             |           | √         | √         | √                | V             | $\sqrt{}$     | $\sqrt{}$                 |

| Power-fail/Precision Reset |           | √         | √         | √                | V             | √             | √                         |

| Power-fail Interrupt       |           | √         | √         | √                | V             | √             | √                         |

| Data Pointers              | 2         | 2         | 2         | 2                | 2             | 2             | 2                         |

| Data Pointer Decrement     |           |           |           |                  |               |               | √                         |

| Power Management Modes     |           |           |           | √                | V             | √             | √                         |

| Ring Oscillator            |           | V         | V         | V                | V             | <b>√</b>      | √                         |

| EMI Reduction Mode         |           |           |           | V                | V             | V             | √                         |

| Real-Time Clock            |           |           |           |                  |               | V             |                           |

| Nonvolatile SRAM           |           |           |           |                  |               | V             |                           |

| Pulse Width Modulation     |           |           |           |                  |               |               | 4 8-bit<br>or<br>2 16-bit |

| A/D Converter              |           |           |           |                  |               |               | 8 Channels<br>10-bit      |

| Operating Voltage          | 4.5V-5.5V | 4.5V-5.5V | 2.7V-5.5V | 4.5V-5.5V        | 4.5V-5.5V     | 4.5V-5.5V     | 4.5V-5.5V                 |

6 of 172 092299

#### SECTION 4: PROGRAMMING MODEL

This section provides a programmer's overview of the High-Speed Microcontroller core. It includes information on the memory map, on-chip RAM, Special Function Registers (SFRs), and instruction set. The programming model of the High-Speed Microcontroller is very similar to that of the industry standard 80C52. The memory map is identical. It uses the same instruction set, though instruction timing is improved. Several new SFRs have been added.

### MEMORY ORGANIZATION

The High-Speed Microcontroller, like the 8052, uses several distant memory areas. These are Registers, program memory, and data memory. Registers serve to control on-chip peripherals and as RAM. Note that registers (on-chip RAM) are separate from data memory. Registers are divided into three categories including directly addressed on-chip RAM, indirectly addressed on-chip RAM, and Special Function Registers. The program and data memory areas are discussed under Memory Map. The Registers are discussed under Registers Map.

### **MEMORY MAP**

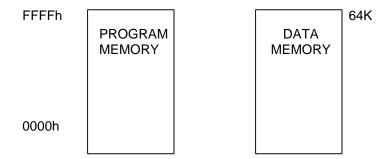

The High-Speed Microcontroller uses a memory addressing scheme that separates program memory (ROM) from data memory (RAM). Each area is 64KB beginning at address 0000h and ending at FFFFh as shown in Figure 4-1. The program and data segments can overlap since they are accessed in different ways. Program memory is fetched by the microcontroller automatically. These addresses are never written by software. In fact, there are no instructions that allow the ROM area to be written. There is one instruction (MOVC) that is used to explicitly read the program area. This is commonly used to read look-up tables. The data memory area is accessed explicitly using the MOVX instruction. This instruction provides multiple ways of specifying the target address. It is used to access the 64KB of data memory.

The address and data range of devices with on-chip program and data memory overlap the 64K memory space. When on-chip memory is enabled, accessing memory in the on-chip range will cause the device to access internal memory. Memory accesses beyond the internal range will be addressed externally via ports 0 and 2.

The ROMSIZE feature allows software to dynamically configure the maximum address of on-chip program memory. This allows the device to act as a bootstrap loader for an external Flash or Nonvolatile SRAM. Secondly, this method can also be used to increase the amount of available program memory from 64KB to 80KB without bank switching. For more information on this feature, please consult Section 6.

Program and data memory can also be increased beyond the 64KB limit using bank switching techniques. This is described in Application Note 81, Memory Expansion with the High-Speed Microcontroller family.

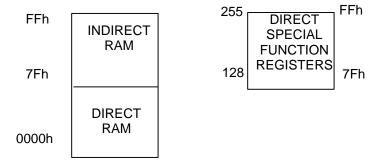

### REGISTER MAP

The Register Map is illustrated in Figure 4-2. It is entirely separate from the program and data memory areas mentioned above. A separate class of instructions is used to access the registers. There are 256 potential register location values. In practice, the High-Speed Microcontroller has 256 bytes of Scratchpad RAM and up to 128 Special Function Registers (SFRs). This is possible since the upper 128 Scratchpad RAM locations can only be accessed indirectly. That is, the contents of a Working Register (described below) will designate the RAM location. Thus a direct reference to one of the upper 128 locations must be an SFR access. Direct RAM is reached at locations 0 to 7Fh (0 to 127).

7 of 172 092299

SFRs are accessed directly between 80h and FFh (128 to 255). The RAM locations between 128 and 255 can be reached through an indirect reference to those locations.

Scratchpad RAM is available for general purpose data storage. It is commonly used in place of off-chip RAM when the total data contents are small. When off-chip RAM is needed, the Scratchpad area will still provide the fastest general purpose access. Within the 256 bytes of RAM, there are several special purpose areas. These are described as follows:

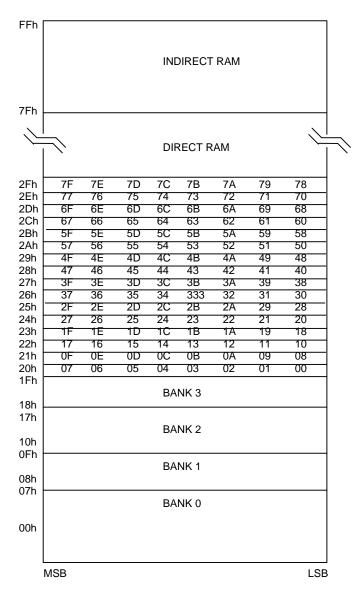

### **Bit Addressable Locations**

In addition to direct register access, some individual bits are also accessible. These are individually addressable bits in both the RAM and SFR area. In the Scratchpad RAM area, registers 20h to 2Fh are bit addressable. This provides 126 (16 \* 8) individual bits available to software. A bit access is distinguished from a full register access by the type of instruction. Addressing modes are discussed in Section 5. In the SFR area, any register location ending in a 0 or 8 is bit addressable. Figure 4-3 shows details of the on-chip RAM addressing including the locations of individual RAM bits.

### **Working Registers**

As part of the lower 128 bytes of RAM, there are four banks of Working Registers (each). The Working registers are general purpose RAM locations that can be addressed in a special way. They are designated R0 through R7. Since there are four banks, the currently selected bank will be used by any instruction using R0-R7. This allows software to change context by simply switching banks. This is controlled via the Program Status Word register in the SFR area described below. The Working Registers also allow their contents to be used for indirect addressing of the upper 128 bytes of RAM. Thus an instruction can designate the value stored in R0 (for example) to address the upper RAM. This value might be the result of another calculation.

### Stack

Another use of the Scratchpad area is for the programmer's stack. This area is selected using the Stack Pointer (SP;81h) SFR. Whenever a call or interrupt is invoked, the return address is placed on the Stack. It also is available to the programmer for variables, etc. since the Stack can be moved, there is no fixed location within the RAM designated as Stack. The Stack Pointer will default to 07h on reset. The user can then move it as needed. A convenient location would be the upper RAM area (>7Fh) since this is only available indirectly. The SP will point to the last used value. Therefore, the next value placed on the Stack is put at SP + 1. Each PUSH or CALL will increment the SP by the appropriate value. Each POP or RET will decrement as well.

## MEMORY MAP Figure 4-1

## **REGISTER MAP** Figure 4-2

## **SCRATCHPAD REGISTER ADDRESSING** Figure 4-3

### SPECIAL FUNCTION REGISTERS

The High-Speed Microcontroller, like the 8051, uses Special Function Registers (SFRs) to control peripherals and modes. In many cases, an SFR will control individual functions or report status on individual functions. The SFRs reside in register locations 80h-FFh and are reached using direct addressing. SFRs that end in 0 or 8 are bit addressable.

All standard SFR locations from the original 8051 are duplicated in the High-Speed Microcontroller, with several additions. Following tables illustrate the locations of the SFRs for various devices. Following each tables a description of the default reset conditions of all SFR bits. The following section is a detailed description of each Special Function Register.

### **DS80C310 SPECIAL FUNCTION REGISTER LOCATIONS** Table 4-1

| REGISTER | BIT 7    | BIT 6 | BIT 5 | BIT 4 | BIT 3 | BIT 2 | BIT 1 | BIT 0  | ADDRESS |

|----------|----------|-------|-------|-------|-------|-------|-------|--------|---------|

| SP       |          |       |       |       |       |       |       |        | 81h     |

| DPL      |          |       |       |       |       |       |       |        | 82h     |

| DPH      |          |       |       |       |       |       |       |        | 83h     |

| DPL1     |          |       |       |       |       |       |       |        | 84h     |

| DPH1     |          |       |       |       |       |       |       |        | 85h     |

| DPS      | 0        | 0     | 0     | 0     | 0     | 0     | 0     | SEL    | 86h     |

| PCON     | SMOD-0   | SMOD0 | -     | -     | GF1   | GF0   | STOP  | IDLE   | 87h     |

| TCON     | TF1      | TR1   | TF0   | TR0   | IE1   | IT1   | IE0   | IT0    | 88h     |

| TMOD     | GATE     | C/T   | M1    | M0    | GATE  | C/T   | M1    | M0     | 89h     |

| TL0      |          |       |       |       |       |       |       |        | 8Ah     |

| TL1      |          |       |       |       |       |       |       |        | 8Bh     |

| TH0      |          |       |       |       |       |       |       |        | 8Ch     |

| TH1      |          |       |       |       |       |       |       |        | 8Dh     |

| CKCON    | -        | -     | T2M   | T1M   | TOM   | MD2   | MD1   | MD0    | 8Eh     |

| P1       | P1.7     | P1.6  | P1.5  | P1.4  | P1.3  | P1.2  | P1.1  | P1.0   | 90h     |

| EXIF     | IE5      | IE4   | IE3   | IE2   | -     | -     | -     | -      | 91h     |

| SCON0    | SM0/FE_0 | SM1_0 | SM2_0 | REN_0 | TB8_0 | RB8_0 | TI_0  | RI_0   | 98h     |

| SBUF0    |          |       |       |       |       |       |       |        | 99h     |

| P2       | P2.7     | P2.6  | P2.5  | P2.4  | P2.3  | P2.2  | P2.1  | P2.0   | A0h     |

| IE       | EA       | -     | ET2   | ES0   | ET1   | EX1   | ET0   | EX0    | A8h     |

| SADDR0   |          |       |       |       |       |       |       |        | A9h     |

| P3       | P3.7     | P3.6  | P3.5  | P3.4  | P3.3  | P3.2  | P3.1  | P3.0   | B0h     |

| IP       | -        | -     | PT2   | PS0   | PT1   | PX1   | PT0   | PX0    | B8h     |

| SADEN0   |          |       |       |       |       |       |       |        | B9h     |

| STATUS   | 0        | HIP   | LIP   | 1     | 1     | 1     | 1     | 1      | C5h     |

| T2CON    | TF2      | EXF2  | RCLK  | TCLK  | EXEN2 | TR2   | C/T2  | CP/RL2 | C8h     |

| T2MOD    | -        | -     | -     | -     | -     | -     | T2OE  | DCEN   | C9h     |

| RCAP2L   |          |       |       |       |       |       |       |        | CAh     |

| RCAP2H   |          |       |       |       |       |       |       |        | CBh     |

| TL2      |          |       |       |       |       |       |       |        | CCh     |

| TH2      |          |       |       |       |       |       |       |        | CDh     |

| PSW      | CY       | AC    | F0    | RS1   | RS0   | OV    | F1    | P      | D0h     |

| WDCON    | -        | POR   | -     | -     | -     | -     | -     | -      | D8h     |

| ACC      |          |       | _     |       |       |       |       |        | E0h     |

| EIE      | -        | -     | -     | -     | EX5   | EX4   | EX3   | EX2    | E8h     |

| В        |          |       |       |       |       |       |       |        | F0h     |

| EIP      | -        | -     | =     | -     | PX5   | PX4   | PX3   | PX2    | F8h     |

## S80C310 SPECIAL FUNCTION REGISTER RESET VALUES Tables 4-2

|          |       |         |       |       | DYES  |       |       | DIES T |         |

|----------|-------|---------|-------|-------|-------|-------|-------|--------|---------|

| REGISTER | BIT 7 | BIT 6   | BIT 5 | BIT 4 | BIT 3 | BIT 2 | BIT 1 | BIT 0  | ADDRESS |

| SP       | 0     | 0       | 0     | 0     | 0     | 1     | 1     | 1      | 81h     |

| DPL      | 0     | 0       | 0     | 0     | 0     | 0     | 0     | 0      | 82h     |

| DPH      | 0     | 0       | 0     | 0     | 0     | 0     | 0     | 0      | 83h     |

| DPL1     | 0     | 0       | 0     | 0     | 0     | 0     | 0     | 0      | 84h     |

| DPH1     | 0     | 0       | 0     | 0     | 0     | 0     | 0     | 0      | 85h     |

| DPS      | 0     | 0       | 0     | 0     | 0     | 0     | 0     | 0      | 86h     |

| PCON     | 0     | 0       | -     | -     | 0     | 0     | 0     | 0      | 87h     |

| TCON     | 0     | 0       | 0     | 0     | 0     | 0     | 0     | 0      | 88h     |

| TMOD     | 0     | 0       | 0     | 0     | 0     | 0     | 0     | 0      | 89h     |

| TL0      | 0     | 0       | 0     | 0     | 0     | 0     | 0     | 0      | 8Ah     |

| TL1      | 0     | 0       | 0     | 0     | 0     | 0     | 0     | 0      | 8Bh     |

| TH0      | 0     | 0       | 0     | 0     | 0     | 0     | 0     | 0      | 8Ch     |

| TH1      | 0     | 0       | 0     | 0     | 0     | 0     | 0     | 0      | 8Dh     |

| CKCON    | -     | -       | 0     | 0     | 0     | 0     | 0     | 1      | 8Eh     |

| P1       | 1     | 1       | 1     | 1     | 1     | 1     | 1     | 1      | 90h     |

| EXIF     | 0     | 0       | 0     | 0     | -     | -     | -     | -      | 91h     |

| SCON0    | 0     | 0       | 0     | 0     | 0     | 0     | 0     | 0      | 98h     |

| SBUF0    | 0     | 0       | 0     | 0     | 0     | 0     | 0     | 0      | 99h     |

| P2       | 1     | 1       | 1     | 1     | 1     | 1     | 1     | 1      | A0h     |

| IE       | 0     | -       | 0     | 0     | 0     | 0     | 0     | 0      | A8h     |

| SADDR0   | 0     | 0       | 0     | 0     | 0     | 0     | 0     | 0      | A9h     |

| P3       | 1     | 1       | 1     | 1     | 1     | 1     | 1     | 1      | B0h     |

| IP       | -     | -       | 0     | 0     | 0     | 0     | 0     | 0      | B8h     |

| SADEN0   | 0     | 0       | 0     | 0     | 0     | 0     | 0     | 0      | B9h     |

| STATUS   | 0     | 0       | 0     | 1     | 1     | 1     | 1     | 1      | C5h     |

| T2CON    | 0     | 0       | 0     | 0     | 0     | 0     | 0     | 0      | C8h     |

| T2MOD    | -     | -       | -     | -     | -     | -     | 0     | 0      | C9h     |

| RCAP2L   | 0     | 0       | 0     | 0     | 0     | 0     | 0     | 0      | CAh     |

| RCAP2H   | 0     | 0       | 0     | 0     | 0     | 0     | 0     | 0      | CBh     |

| TL2      | 0     | 0       | 0     | 0     | 0     | 0     | 0     | 0      | CCh     |

| TH2      | 0     | 0       | 0     | 0     | 0     | 0     | 0     | 0      | CDh     |

| PSW      | 0     | 0       | 0     | 0     | 0     | 0     | 0     | 0      | D0h     |

| WDCON    | -     | SPECIAL | -     | -     | -     | -     | -     | -      | D8h     |

| ACC      | 0     | 0       | 0     | 0     | 0     | 0     | 0     | 0      | E0h     |

| EIE      | -     | -       | -     | -     | 0     | 0     | 0     | 0      | E8h     |

| В        | 0     | 0       | 0     | 0     | 0     | 0     | 0     | 0      | F0h     |

| EIP      | -     | -       | -     | -     | 0     | 0     | 0     | 0      | F8h     |

## DS80C320/DS80C323 SPECIAL FUNCTION REGISTER LOCATIONS

Table 4-3

| REGISTER | BIT 7    | BIT 6 | BIT 5 | BIT 4 | BIT 3 | BIT 2 | BIT 1 | BIT 0  | ADDRESS |

|----------|----------|-------|-------|-------|-------|-------|-------|--------|---------|

| SP       | DII /    | DII U | DITS  | DIIT  | DII 3 | BII 2 | DIII  | BITO   | 81h     |

| DPL      |          |       |       |       |       |       |       |        | 82h     |

| DPH      |          |       |       |       |       |       |       |        | 83h     |

| DPL1     |          |       |       |       |       |       |       |        | 84h     |

| DPH1     |          |       |       |       |       |       |       |        | 85h     |

| DPS      | 0        | 0     | 0     | 0     | 0     | 0     | 0     | SEL    | 86h     |

| PCON     | SMOD_0   | SMOD0 | -     | -     | GF1   | GF0   | STOP  | IDLE   | 87h     |

| TCON     | TF1      | TR1   | TF0   | TR0   | IE1   | IT1   | IE0   | ITO    | 88h     |

| TMOD     | GATE     | C/T   | M1    | M0    | GATE  | C/T   | M1    | M0     | 89h     |

|          | GATE     | C/T   | 1111  | IVIO  | OAIL  | C/T   | 1411  | IVIO   |         |

| TL0      |          |       |       |       |       |       |       |        | 8Ah     |

| TL1      |          |       |       |       |       |       |       |        | 8Bh     |

| TH0      |          |       |       |       |       |       |       |        | 8Ch     |

| TH1      |          |       |       |       |       |       |       |        | 8Dh     |

| CKCON    | WD1      | WD0   | T2M   | T1M   | T0M   | MD2   | MD1   | MD0    | 8Eh     |

| P1       | P1.7     | P1.6  | P1.5  | P1.4  | P1.3  | P1.2  | P1.1  | P1.0   | 90h     |

| EXIF     | IE5      | IE4   | IE3   | IE2   | -     | RGMD  | RGSL  | BGS    | 91h     |

| SCON0    | SM0/FE_0 | SM1_0 | SM2_0 | REN_0 | TB8_0 | RB8_0 | TI_0  | RI_0   | 98h     |

| SBUF0    |          |       |       |       |       |       |       |        | 99h     |

| P2       | P2.7     | P2.6  | P2.5  | P2.4  | P2.3  | P2.2  | P2.1  | P2.0   | A0h     |

| IE       | EA       | ES1   | ET2   | ES0   | ET1   | EX1   | ET0   | EX0    | A8h     |

| SADDR0   |          |       |       |       |       |       |       |        | A9h     |

| SADDR1   |          |       |       |       |       |       |       |        | AAh     |

| P3       | P3.7     | P3.6  | P3.5  | P3.4  | P3.3  | P3.2  | P3.1  | P3.0   | B0h     |

| IP       | -        | PS1   | PT2   | PS0   | PT1   | PX1   | PT-   | PX0    | B8h     |

| SADEN0   |          |       |       |       |       |       |       |        | B9h     |

| SADEN1   |          |       |       |       |       |       |       |        | Bah     |

| SCON1    | SMO/FE_1 | SM1_1 | SM2_1 | REN_1 | TB8_1 | RB8_1 | I1_1  | R1_1   | C0h     |

| SBUF1    |          |       |       |       |       |       |       |        | C1h     |

| STATUS   | PIP      | HIP   | LIP   | 1     | 1     | 1     | 1     | 1      | C5h     |

| TA       |          |       |       |       |       |       |       |        | C7h     |

| T2CON    | TF2      | EXF2  | RCLK  | TCLK  | EXEN2 | TR2   | C/T2  | CP/RL2 | C8h     |

| T2MOD    | -        | -     | -     | -     | -     | -     | T2OE  | DCEN   | C9h     |

| RCAP2L   |          |       |       |       |       |       |       |        | CAh     |

| RCAP2H   |          |       |       |       |       |       |       |        | CBh     |

| TL2      |          |       |       |       |       |       |       |        | CCh     |

| TH2      |          |       |       |       |       | 1     |       |        | CDh     |

| PSW      | CY       | AC    | F0    | RS1   | RS0   | OV    | F1    | P      | D0h     |

| WDCON    | SMOD 1   | POR   | EPF1  | PF1   | WDIF  | WTRF  | EWT   | RWT    | D8h     |

| ACC      | _        |       |       |       |       |       |       |        | E0h     |

| EIE      | -        | -     | -     | EWDI  | EX5   | EX4   | EX3   | EX2    | E8h     |

| В        |          |       |       |       |       | 1     |       |        | F0h     |

| EIP      | -        | -     | -     | PWDI  | PX5   | PX4   | PX3   | PX2    | F8h     |

Shaded bits are Timed Access protected

## DS80C320/DS80C323 SPECIAL FUNCTION REGISTER RESET VALUES

## Table 4-4

| REGISTER | BIT 7 | BIT 6   | BIT 5 | BIT 4   | BIT 3 | BIT 2   | BIT 1   | BIT 0 | ADDRESS |

|----------|-------|---------|-------|---------|-------|---------|---------|-------|---------|

| SP       | 0     | 0       | 0     | 0       | 0     | 0       | 0       | 0     | 81h     |

| DPL      | 0     | 0       | 0     | 0       | 0     | 0       | 0       | 0     | 82h     |

| DPH      | 0     | 0       | 0     | 0       | 0     | 0       | 0       | 0     | 83h     |

| DPL1     | 0     | 0       | 0     | 0       | 0     | 0       | 0       | 0     | 84h     |

| DPH1     | 0     | 0       | 0     | 0       | 0     | 0       | 0       | 0     | 85h     |

| DPS      | 0     | 0       | 0     | 0       | 0     | 0       | 0       | 0     | 86h     |

| PCON     | 0     | 0       | -     | -       | 0     | 0       | 0       | 0     | 87h     |

| TCON     | 0     | 0       | 0     | 0       | 0     | 0       | 0       | 0     | 88h     |

| TMOD     | 0     | 0       | 0     | 0       | 0     | 0       | 0       | 0     | 89h     |

| TL0      | 0     | 0       | 0     | 0       | 0     | 0       | 0       | 0     | 8Ah     |

| TL1      | 0     | 0       | 0     | 0       | 0     | 0       | 0       | 0     | 8Bh     |

| TH0      | 0     | 0       | 0     | 0       | 0     | 0       | 0       | 0     | 8Ch     |

| TH1      | 0     | 0       | 0     | 0       | 0     | 0       | 0       | 0     | 8Dh     |

| CKCON    | 0     | 0       | 0     | 0       | 0     | 0       | 0       | 0     | 8Eh     |

| P1       | 1     | 1       | 0     | 0       | 0     | 0       | 0       | 0     | 90h     |

| EXIF     | 0     | 0       | 0     | 0       | 0     | 0       | 0       | 0     | 91h     |

| SCON0    | 0     | 0       | 0     | 0       | 0     | 0       | 0       | 0     | 98h     |

| SBUF0    | 0     | 0       | 0     | 0       | 0     | 0       | 0       | 0     | 99h     |

| P2       | 1     | 1       | 1     | 1       | 1     | 1       | 1       | 1     | A0h     |

| IE       | 0     | 0       | 0     | 0       | 0     | 0       | 0       | 0     | A8h     |

| SADDR0   | 0     | 0       | 0     | 0       | 0     | 0       | 0       | 0     | A9h     |

| SADDR1   | 0     | 0       | 0     | 0       | 0     | 0       | 0       | 0     | AAh     |

| P3       | 1     | 1       | 1     | 1       | 1     | 1       | 1       | 1     | B0h     |

| IP       | -     | 0       | 0     | 0       | 0     | 0       | 0       | 0     | B8h     |

| SADEN0   | 0     | 0       | 0     | 0       | 0     | 0       | 0       | 0     | B9h     |

| SADEN1   | 0     | 0       | 0     | 0       | 0     | 0       | 0       | 0     | BAh     |

| SCON1    | 0     | 0       | 0     | 0       | 0     | 0       | 0       | 0     | C0h     |

| SBUF1    | 0     | 0       | 0     | 0       | 0     | 0       | 0       | 0     | C1h     |

| STATUS   | 0     | 0       | 0     | 1       | 1     | 1       | 1       | 1     | C5h     |

| TA       | 1     | 1       | 1     | 1       | 1     | 1       | 1       | 1     | C7h     |

| T2CON    | 0     | 0       | 0     | 0       | 0     | 0       | 0       | 0     | C8h     |

| T2MOD    | -     | -       | -     | -       | -     | -       | 0       | 0     | C9h     |

| RCAP2L   | 0     | 0       | 0     | 0       | 0     | 0       | 0       | 0     | CAh     |

| RCAP2H   | 0     | 0       | 0     | 0       | 0     | 0       | 0       | 0     | CBh     |

| TL2      | 0     | 0       | 0     | 0       | 0     | 0       | 0       | 0     | CCh     |

| TH2      | 0     | 0       | 0     | 0       | 0     | 0       | 0       | 0     | CDh     |

| PSW      | 0     | 0       | 0     | 0       | 0     | 0       | 0       | 0     | D0h     |

| WDCON    | 0     | SPECIAL | 0     | SPECIAL | 0     | SPECIAL | SPECIAL | 0     | D8h     |

| ACC      | 0     | 0       | 0     | 0       | 0     | 0       | 0       | 0     | E0h     |

| EIE      | -     | -       | -     | -       | 0     | 0       | 0       | 0     | E8h     |

| В        | 0     | 0       | 0     | 0       | 0     | 0       | 0       | 0     | F0h     |

| EIP      |       | -       | -     | 0       | 0     | 0       | 0       | 0     | F8h     |

## DS83C520/DS87C520 SPECIAL FUNCTION REGISTER LOCATIONS

Table 4-5

| REGISTER | BIT 7    | BIT 6 | BIT 5 | BIT 4   | BIT 3              | BIT 2  | BIT 1 | BIT 0  | ADDRESS |

|----------|----------|-------|-------|---------|--------------------|--------|-------|--------|---------|

| P0       | P0.7     | P0.6  | P0.5  | P0.4    | P0.3               | P0.2   | P0.1  | P0.0   | 80h     |

| SP       |          |       |       |         |                    |        |       |        | 81h     |

| DPL      |          |       |       |         |                    |        |       |        | 82h     |

| DPH      |          |       |       |         |                    |        |       |        | 83h     |

| DPL1     |          |       |       |         |                    |        |       |        | 84h     |

| DPH1     |          |       |       |         |                    |        |       |        | 85h     |

| DPS      | 0        | 0     | 0     | 0       | 0                  | 0      | 0     | SEL    | 86h     |

| PCON     | SMOD_0   | SMOD0 | -     | -       | GF1                | GF0    | STOP  | IDLE   | 87h     |

| TCON     | TF1      | TR1   | TF0   | TR0     | IE1                | IT1    | IE0   | IT0    | 88h     |

| TMOD     | GATE     | C/T   | M1    | M0      | GATE               | C/T    | M1    | M0     | 89h     |

| TL0      |          |       |       |         |                    |        |       |        | 8Ah     |

| TL1      |          |       |       |         |                    |        |       |        | 8Bh     |

| TH0      |          |       |       |         |                    |        |       |        | 8Ch     |

| TH1      |          |       |       |         |                    |        |       |        | 8Dh     |

| CKCON    | WD1      | WD0   | T2M   | T1M     | T0M                | MD2    | MD1   | MD0    | 8Eh     |

| P1       | P1.7     | P1.6  | P1.5  | P1.4    | P1.3               | P1.2   | P1.1  | P1.0   | 90h     |

| EXIF     | IE5      | IE4   | IE3   | IE2     | $XT/\overline{RG}$ | RGMD   | RGSL  | BGS    | 91h     |

| SCON0    | SM0/FE_0 | SM1_0 | SM2_0 | REN_0   | TB8_0              | RB8_0  | TI_0  | RI_0   | 98h     |

| SBUF0    |          |       |       |         |                    |        |       |        | 99h     |

| P2       | P2.7     | P2.6  | P2.5  | P2.4    | P2.3               | P2.2   | P2.1  | P2.0   | A0h     |

| IE       | EA       | ES1   | ET2   | ES0     | ET1                | EX1    | ET0   | EX0    | A8h     |

| SADDR0   |          |       |       |         |                    |        |       |        | A9h     |

| SADDR1   |          |       |       |         |                    |        |       |        | AAh     |

| P3       | P3.7     | P3.6  | P3.5  | P3.4    | P3.3               | P3.2   | P3.1  | P3.0   | B0h     |

| IP       | -        | PS1   | PT2   | PS0     | PT1                | PX1    | PT0   | PX0    | B8h     |

| SADEN0   |          |       |       |         |                    |        |       |        | B9h     |

| SADEN1   |          |       |       |         |                    |        |       |        | BAh     |

| SCON1    | SM0/FE_1 | SM1_1 | SM2_1 | REN_1   | TB8_1              | RB8_1  | TI_1  | RI_1   | C0h     |

| SBUF1    |          |       |       |         |                    |        |       |        | C1h     |

| ROMSIZE  | -        | -     | -     | -       | -                  | RMS2   | RMS1  | RMS0   | C2h     |

| PMR      | CD1      | CD0   | SWB   | -       | XTOFF              | ALEOFF | DME1  | DME0   | C4h     |

| STATUS   | PIP      | HIP   | LIP   | XTUP    | SPTA1              | SPRA1  | SPTA0 | SPRA0  | C5h     |

| TA       |          |       |       |         |                    |        |       |        | C7h     |

| T2CON    | TF2      | EXF2  | RCLK  | TCLK    | EXEN2              | TR2    | C/T2  | CP/RL2 | C8h     |

| T2MOD    | -        | -     | -     | -       | -                  | -      | T2OE  | DCEN   | C9h     |

| RCAP2L   |          |       |       |         |                    |        |       |        | CAh     |

| RCAP2H   |          |       |       |         |                    |        |       |        | CBh     |

| TL2      |          |       |       |         |                    |        | 1     |        | CCh     |

| TH2      |          |       |       |         | 7.70               | 1077   | ļ     | _      | CDh     |

| PSW      | CY       | AC    | F0    | RS1     | RS0                | OV     | F1    | P      | D0h     |

| WDCON    | SMOD_1   | POR   | EPFI  | PFI     | WDIF               | WTRF   | EWT   | RWT    | D8h     |

| ACC      |          |       |       | -       | 777.2              |        | T77.5 | F712   | E0h     |

| EIE      | -        | -     | -     | EWDI    | EX5                | EX4    | EX3   | EX2    | E8h     |

| В        |          |       |       | DIVID 1 | DV.                | DV/4   | DYZ   | DV2    | F0h     |

| EIP      | -        | -     | -     | PWD1    | PX5                | PX4    | PX3   | PX2    | F8h     |

Shaded bits are Timed Access protected

## DS83C520/DS87C520 SPECIAL FUNCTION REGISTER RESET VALUES

## Table 4-6

| REGISTER | BIT 7 | BIT 6   | BIT 5 | BIT 4   | BIT 3   | BIT 2   | BIT 1   | BIT 0 | ADDRESS |

|----------|-------|---------|-------|---------|---------|---------|---------|-------|---------|

| P0       | 1     | 1       | 1     | 1       | 1       | 1       | 1       | 1     | 80h     |

| SP       | 0     | 0       | 0     | 0       | 0       | 1       | 1       | 1     | 81h     |

| DPL      | 0     | 0       | 0     | 0       | 0       | 0       | 0       | 0     | 82h     |

| DPH      | 0     | 0       | 0     | 0       | 0       | 0       | 0       | 0     | 83h     |

| DPL1     | 0     | 0       | 0     | 0       | 0       | 0       | 0       | 0     | 84h     |

| DPH1     | 0     | 0       | 0     | 0       | 0       | 0       | 0       | 0     | 85h     |

| DPS      | 0     | 0       | 0     | 0       | 0       | 0       | 0       | 0     | 86h     |

| PCON     | 0     | 0       | -     | -       | 0       | 0       | 0       | 0     | 87h     |

| TCON     | 0     | 0       | 0     | 0       | 0       | 0       | 0       | 0     | 88h     |

| TMOD     | 0     | 0       | 0     | 0       | 0       | 0       | 0       | 0     | 89h     |

| TL0      | 0     | 0       | 0     | 0       | 0       | 0       | 0       | 0     | 8Ah     |

| TL1      | 0     | 0       | 0     | 0       | 0       | 0       | 0       | 0     | 8Bh     |

| TH0      | 0     | 0       | 0     | 0       | 0       | 0       | 0       | 0     | 8Ch     |

| TH1      | 0     | 0       | 0     | 0       | 0       | 0       | 0       | 0     | 8Dh     |

|          | 0     |         |       |         |         | _       |         |       | 8Eh     |

| CKCON    | 1     | 0       | 0     | 0       | 0       | 0       | 0       | 1     |         |

| P1       |       | 1       | 1     |         |         |         | -       |       | 90h     |

| EXIF     | 0     | 0       | 0     | 0       | SPECIAL | SPECIAL | SPECIAL | 0     | 91h     |

| SCON0    | 0     | 0       | 0     | 0       | 0       | 0       | 0       | 0     | 98h     |

| SBUF0    | 0     | 0       | 0     | 0       | 0       | 0       | 0       | 0     | 99h     |

| P2       | 1     | 1       | 1     | 1       | 1       | 1       | 1       | 1     | A0h     |

| IE       | 0     | 0       | 0     | 0       | 0       | 0       | 0       | 0     | A8h     |

| SADDR0   | 0     | 0       | 0     | 0       | 0       | 0       | 0       | 0     | A9h     |

| SADDR1   | 0     | 0       | 0     | 0       | 0       | 0       | 0       | 0     | AAh     |

| P3       | 1     | 1       | 1     | 1       | 1       | 1       | 1       | 1     | B0h     |

| IP       | -     | 0       | 0     | 0       | 0       | 0       | 0       | 0     | B8h     |

| SADEN0   | 0     | 0       | 0     | 0       | 0       | 0       | 0       | 0     | B9h     |

| SADEN1   | 0     | 0       | 0     | 0       | 0       | 0       | 0       | 0     | BAh     |

| SCON1    | 0     | 0       | 0     | 0       | 0       | 0       | 0       | 0     | C0h     |

| SBUF1    | 0     | 0       | 0     | 0       | 0       | 0       | 0       | 0     | C1h     |

| ROMSIZE  | -     | -       | -     | -       | -       | 1       | 0       | 1     | C2h     |

| PMR      | 0     | 1       | 0     | -       | 0       | 0       | 0       | 0     | C4h     |

| STATUS   | 0     | 0       | 0     | SPECIAL | 0       | 0       | 0       | 0     | C5h     |

| TA       | 1     | 1       | 1     | 1       | 1       | 1       | 1       | 1     | C7h     |

| T2CON    | 0     | 0       | 0     | 0       | 0       | 0       | 0       | 0     | C8h     |

| T2MOD    | ı     | -       | -     | -       | ı       | -       | 0       | 0     | C9h     |

| RCAP2L   | 0     | 0       | 0     | 0       | 0       | 0       | 0       | 0     | CAh     |

| RCAP2H   | 0     | 0       | 0     | 0       | 0       | 0       | 0       | 0     | CBh     |

| TL2      | 0     | 0       | 0     | 0       | 0       | 0       | 0       | 0     | CCh     |

| TH2      | 0     | 0       | 0     | 0       | 0       | 0       | 0       | 0     | CDh     |

| PSW      | 0     | 0       | 0     | 0       | 0       | 0       | 0       | 0     | D0h     |

| WDCON    | 0     | SPECIAL | 0     | SPECIAL | 0       | SPECIAL | SPECIAL | 0     | D8h     |

| ACC      | 0     | 0       | 0     | 0       | 0       | 0       | 0       | 0     | E0h     |

| EIE      | -     | -       | -     | 0       | 0       | 0       | 0       | 0     | E8h     |

| В        | 0     | 0       | 0     | 0       | 0       | 0       | 0       | 0     | F0h     |

| EIP      | -     | -       | _     | 0       | 0       | 0       | 0       | 0     | F8h     |

## DS87C530 SPECIAL FUNCTION REGISTER LOCATION Tables 4-7

| D001 000 |              |               |         |        |         |               | т     | т      |         |

|----------|--------------|---------------|---------|--------|---------|---------------|-------|--------|---------|

| REGISTER | BIT 7        | BIT 6         | BIT 5   | BIT 4  | BIT 3   | BIT 2         | BIT 1 | BIT 0  | ADDRESS |

| P0       | P0.7         | P0.6          | P0.5    | P0.4   | P0.3    | P0.2          | P0.1  | P0.0   | 80h     |

| SP       |              |               |         |        |         |               |       |        | 81h     |

| DPL      |              |               |         |        |         |               |       |        | 82h     |

| DPH      |              |               |         |        |         |               |       |        | 83h     |

| DPL1     |              |               |         |        |         |               |       |        | 84h     |

| DPH1     |              |               |         |        |         |               |       |        | 85h     |

| DPS      | 0            | 0             | 0       | 0      | 0       | 0             | 0     | SEL    | 86h     |

| PCON     | SMOD_0       | SMOD0         | -       | -      | GF1     | GF0           | STOP  | IDLE   | 87h     |

| TCON     | TF1          | TR1           | TF0     | TR0    | IE1     | IT1           | IE0   | IT0    | 88h     |

| TMOD     | GATE         | C/T           | M1      | M0     | GATE    | C/T           | M1    | M0     | 89h     |

| TL0      |              |               |         |        |         |               |       |        | 8Ah     |

| TL1      |              |               |         |        |         |               |       |        | 8Bh     |

| TH0      |              |               |         |        |         |               |       |        | 8Ch     |

| TH1      |              |               |         |        |         |               |       |        | 8Dh     |

| CKCON    | WD1          | WD0           | T2M     | T1M    | TOM     | MD2           | MD1   | MD0    | 8Eh     |

| P1       | P1.7         | P1.6          | P1.5    | P1.4   | P1.3    | P1.2          | P1.1  | P1.0   | 90h     |

| EXIF     | IE5          | IE4           | IE3     | IE2    | XT/ RG  | RGMD          | RGSL  | BGS    | 91h     |

| TRIM     | E4K          | $X12/\bar{6}$ | TRM2    | TRM2   | TRM1    | TRM1          | TRM0  | TRM0   | 96h     |

| SCON0    | SM0/FE_0     | SM1_0         | SM2_0   | REN_0  | TB8_0   | RB8_0         | TI_0  | RI_0   | 98h     |

| SBUF0    | SMU/FE_U     | SWII_U        | SW12_0  | KEN_U  | 100_0   | KB6_U         | 11_0  | KI_U   | 99h     |

| P2       | P2.7         | P2.6          | P2.5    | P2.4   | P2.3    | P2.2          | P2.1  | P2.0   | A0h     |

| IE       | EA           | ES1           | ET2     | ES0    | ET1     | EX1           | ET0   |        |         |

| SADDR0   | EA           | ESI           | E12     | ESU    | EII     | EXI           | EIU   | EX0    | A8h     |

|          |              |               |         |        |         |               |       |        | A9h     |

| SADDR1   | D2 7         | D2 6          | D2 5    | D2 4   | D2 2    | D2 2          | D2 1  | D2 0   | AAh     |

| P3       | P3.7         | P3.6          | P3.5    | P3.4   | P3.3    | P3.2          | P3.1  | P3.0   | B0h     |

| IP       | -            | PS1           | PT2     | PS0    | PT1     | PX1           | PT0   | PX0    | B8h     |

| SADEN0   |              |               |         |        |         |               |       |        | B9h     |

| SADEN1   | G) (0 (E) (1 | G3.544        | G) (0 1 | DEN. 4 | FFD 0 4 | <b>DD</b> 0.4 | TTY 4 | DY 4   | BAh     |

| SCON1    | SM0/FE_1     | SM1_1         | SM2_1   | REN_1  | TB8_1   | RB8_1         | TI_1  | RI_1   | C0h     |

| SBUF1    |              |               |         |        |         |               |       |        | C1h     |

| ROMSIZE  | -            | -             | -       | -      | -       | RMS2          | RMS1  | RMS0   | C2h     |

| PMR      | CD1          | CD0           | SWB     | -      | XTOFF   | ALEOFF        | DME1  | DME0   | C4h     |

| STATUS   | PIP          | HIP           | LIP     | XTUP   | SPTA1   | SPRA1         | SPTA0 | SPRA0  | C5h     |

| TA       |              |               |         |        |         |               |       |        | C7h     |

| T2CON    | TF2          | EXF2          | RCLK    | TCLK   | EXEN2   | TR2           | C/ T2 | CP/RL2 | C8h     |

| T2MOD    | -            | -             | -       | -      | -       | -             | T2OE  | DCEN   | C9h     |

| RCAP2L   |              |               |         |        |         |               |       |        | CAh     |

| RCAP2H   |              |               |         |        |         |               |       |        | CBh     |

| TL2      |              |               |         |        |         |               |       |        | CCh     |

| TH2      |              |               |         |        |         |               |       |        | CDh     |

| PSW      | CY           | AC            | F0      | RS1    | RS0     | OV            | F1    | P      | D0h     |

| WDCON    | SMOD_0       | POR           | EPFI    | PFI    | WDIF    | WTRF          | EWT   | RWT    | D8h     |

| ACC      | _            |               |         |        |         |               |       |        | E0h     |

| EIE      | _            | -             | ERTCI   | EWDI   | EX5     | EX4           | EX3   | EX2    | E8h     |

| В        |              |               |         |        |         |               | -     |        | F0h     |

| RTASS    |              |               |         |        |         |               |       |        | F2h     |

| RTAS     | 0            | 0             |         |        |         |               |       |        | F3h     |

| RTAM     | 0            | 0             |         |        |         |               |       |        | F4h     |

| RTAH     | 0            | 0             | 0       |        |         |               |       |        | F5h     |

| 1711111  | V            | J             |         | 1      | 1       | 1             | 1     | J.     | 1 511   |

DS87C530 SPECIAL FUNCTION REGISTER LOCATION Tables 4-7( Cont.)

| REGISTER | BIT 7 | BIT 6 | BIT 5 | BIT 4 | BIT 3 | BIT 2 | BIT 1 | BIT 0 | ADDRESS |

|----------|-------|-------|-------|-------|-------|-------|-------|-------|---------|

| EIP      | -     | -     | PRTCI | PWDI  | PX5   | PX4   | PX3   | PX2   | F8h     |

| RTCC     | SSCE  | SCE   | MCE   | HCE   | RTCE  | RTCWE | RTCIF | RTCE  | F9h     |

| RTCSS    |       |       |       |       |       |       |       |       | FAh     |

| RTCS     | 0     | 0     |       |       |       |       |       |       | FBh     |

| RTCM     | 0     | 0     |       |       |       |       |       |       | FCh     |

| RTCH     |       |       |       |       |       |       |       |       | FDh     |

| RTCD0    |       |       |       |       |       |       |       |       | FEh     |

| RTCD1    |       |       |       |       |       |       |       |       | FFh     |

Shaded bits are Timed Access protected

## DS87C530 SPECIAL FUNCTION REGISTER RESET VALUES Tables 4-8

| DS87C530      | ) SPEC             | IAL FU             | l ables            | 4-8                |              |              |                    |                    |            |

|---------------|--------------------|--------------------|--------------------|--------------------|--------------|--------------|--------------------|--------------------|------------|

| REGISTER      | BIT 7              | BIT 6              | BIT 5              | BIT 4              | BIT 3        | BIT 2        | BIT 1              | BIT 0              | ADDRESS    |

| PO            | 1                  | 1                  | 1                  | 1                  | 1            | 1            | 1                  | 1                  | 80h        |

| SP            | 0                  | 0                  | 0                  | 0                  | 0            | 1            | 1                  | 1                  | 81h        |

| DPL           | 0                  | 0                  | 0                  | 0                  | 0            | 0            | 0                  | 0                  | 82h        |

| DPH           | 0                  | 0                  | 0                  | 0                  | 0            | 0            | 0                  | 0                  | 83h        |

| DPL1          | 0                  | 0                  | 0                  | 0                  | 0            | 0            | 0                  | 0                  | 84h        |

| DPH1          | 0                  | 0                  | 0                  | 0                  | 0            | 0            | 0                  | 0                  | 85h        |

| DPS           | 0                  | 0                  | 0                  | 0                  | 0            | 0            | 0                  | 0                  | 86h        |

| PCON          | 0                  | 0                  |                    |                    | 0            | 0            | 0                  | 0                  | 87h        |

|               | 0                  | 0                  | 0                  | - 0                | 0            |              | 0                  |                    |            |

| TCON          |                    |                    |                    |                    |              | 0            |                    | 0                  | 88h        |

| TMOD          | 0                  | 0                  | 0                  | 0                  | 0            | 0            | 0                  | 0                  | 89h        |

| TL0           | 0                  | 0                  | 0                  | 0                  | 0            | 0            | 0                  | 0                  | 8Ah        |

| TL1           | 0                  | 0                  | 0                  | 0                  | 0            | 0            | 0                  | 0                  | 8Bh        |

| TH0           | 0                  | 0                  | 0                  | 0                  | 0            | 0            | 0                  | 0                  | 8Ch        |

| TH1           | 0                  | 0                  | 0                  | 0                  | 0            | 0            | 0                  | 0                  | 8Dh        |

| CKCON         | 0                  | 0                  | 0                  | 0                  | 0            | 0            | 0                  | 1                  | 8Eh        |

| P1            | 1                  | 1                  | 1                  | 1                  | 1            | 1            | 1                  | 1                  | 90h        |

| EXIF          | 0                  | 0                  | 0                  | 0                  | SPECIAL      | SPECIAL      | SPECIAL            | 0                  | 91h        |

| TRIM          | SPECIAL            | SPECIAL            | SPECIAL            | SPECIAL            | SPECIAL      | SPECIAL      | SPECIAL            | SPECIAL            | 96h        |

| SCON0         | 0                  | 0                  | 0                  | 0                  | 0            | 0            | 0                  | 0                  | 98h        |

| SBUF0         | 0                  | 0                  | 0                  | 0                  | 0            | 0            | 0                  | 0                  | 99h        |

| P2            | 1                  | 1                  | 1                  | 1                  | 1            | 1            | 1                  | 1                  | A0h        |

| IE            | 0                  | 0                  | 0                  | 0                  | 0            | 0            | 0                  | 0                  | A8h        |

| SADDR0        | 0                  | 0                  | 0                  | 0                  | 0            | 0            | 0                  | 0                  | A9h        |

| SADDR1        | 0                  | 0                  | 0                  | 0                  | 0            | 0            | 0                  | 0                  | AAh        |

| P3            | 1                  | 1                  | 1                  | 1                  | 1            | 1            | 1                  | 1                  | B0h        |

| IP            | -                  | 0                  | 0                  | 0                  | 0            | 0            | 0                  | 0                  | B8h        |

| SADEN0        | 0                  | 0                  | 0                  | 0                  | 0            | 0            | 0                  | 0                  | B9h        |

| SADEN1        | 0                  | 0                  | 0                  | 0                  | 0            | 0            | 0                  | 0                  | BAh        |

| SCON1         | 0                  | 0                  | 0                  | 0                  | 0            | 0            | 0                  | 0                  | C0h        |

| SBUF1         | 0                  | 0                  | 0                  | 0                  | 0            | 0            | 0                  | 0                  | C1h        |

| ROMSIZE       | -                  | -                  | -                  | -                  | ı            | 1            | 0                  | 1                  | C2h        |

| PMR           | 0                  | 1                  | 0                  | -                  | 0            | 0            | 0                  | 0                  | C4h        |

| STATUS        | 0                  | 0                  | 0                  | SPECIAL            | 0            | 0            | 0                  | 0                  | C5h        |

| TA            | 1                  | 1                  | 1                  | 1                  | 1            | 1            | 1                  | 1                  | C7h        |

| T2CON         | 0                  | 0                  | 0                  | 0                  | 0            | 0            | 0                  | 0                  | C8h        |

| T2MOD         | -                  | -                  | -                  | -                  | =            | -            | 0                  | 0                  | C9h        |

| RCAP2L        | 0                  | 0                  | 0                  | 0                  | 0            | 0            | 0                  | 0                  | CAh        |

| RCAP2H        | 0                  | 0                  | 0                  | 0                  | 0            | 0            | 0                  | 0                  | CBh        |

| TL2           | 0                  | 0                  | 0                  | 0                  | 0            | 0            | 0                  | 0                  | CCh        |

| TH2           | 0                  | 0                  | 0                  | 0                  | 0            | 0            | 0                  | 0                  | CDh        |

| PSW           | 0                  | 0                  | 0                  | 0                  | 0            | 0            | 0                  | 0                  | D0h        |

| WDCON         | 0                  | SPECIAL            | 0                  | SPECIAL            | 0            | SPECIAL      | SPECIAL            | 0                  | D8h        |

| ACC           | 0                  | 0                  | 0                  | 0                  | 0            | 0            | 0                  | 0                  | E0h        |

| EIE           | _                  | _                  | 0                  | 0                  | 0            | 0            | 0                  | 0                  | E8h        |

| В             | 0                  | 0                  | 0                  | 0                  | 0            | 0            | 0                  | 0                  | F0h        |

| RTASS         | SPECIAL            | SPECIAL            | SPECIAL            | SPECIAL            | SPECIAL      | SPECIAL      | SPECIAL            | SPECIAL            | F2h        |

| RTAS          | 0                  | 0                  | SPECIAL            | SPECIAL            | SPECIAL      | SPECIAL      | SPECIAL            | SPECIAL            | F3h        |

| RTAM          | 0                  | 0                  | SPECIAL            | SPECIAL            | SPECIAL      | SPECIAL      | SPECIAL            | SPECIAL            | F4h        |

| RTAH          | 0                  | 0                  | 0                  | SPECIAL            | SPECIAL      | SPECIAL      | SPECIAL            | SPECIAL            | F5h        |

| EIP           | - CDECLAI          | - CDECLAI          | 0                  | 0                  | 0            | 0            | 0                  | 0                  | F8h        |

| RTCC<br>RTCSS | SPECIAL<br>SPECIAL | SPECIAL<br>SPECIAL | SPECIAL<br>SPECIAL | SPECIAL<br>SPECIAL | 0<br>SPECIAL | 0<br>SPECIAL | SPECIAL<br>SPECIAL | SPECIAL<br>SPECIAL | F9h<br>FAh |

| RTCS          | 0                  | 0                  | SPECIAL            | SPECIAL            | SPECIAL      | SPECIAL      | SPECIAL            | SPECIAL            | FBh        |

| RTCM          | 0                  | 0                  | SPECIAL            | SPECIAL            | SPECIAL      | SPECIAL      | SPECIAL            | SPECIAL            | FCh        |

| RTCH          | SPECIAL            | SPECIAL            | SPECIAL            | SPECIAL            | SPECIAL      | SPECIAL      | SPECIAL            | SPECIAL            | FDh        |

| RTCD0         | SPECIAL            | SPECIAL            | SPECIAL            | SPECIAL            | SPECIAL      | SPECIAL      | SPECIAL            | SPECIAL            | FEh        |

|       |         | E 1     |         |         |         |         |         |         |     |  |  |

|-------|---------|---------|---------|---------|---------|---------|---------|---------|-----|--|--|

| RTCD1 | SPECIAL | FFh |  |  |

### SPECIAL FUNCTION REGISTERS

Most of the unique features of the High-Speed Microcontroller family are controlled by bits in special function registers (SFRs) located in unused locations in the 8051 SFR map. This allows for increased functionality while maintaining complete instruction set compatibility.

The description for each bit indicates its read and write access, as well as its state after a power on reset. Bits which are affected by a no-battery reset are also indicated. Note that many bits and registers are unique to specific devices, and their functions will vary between different members of the High-Speed Microcontroller family.

## Port 0 (P0)

|         | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|---------|------|------|------|------|------|------|------|------|

| SFR 80h | P0.7 | P0.6 | P0.5 | P0.4 | P0.3 | P0.2 | P0.1 | P0.0 |

|         | RW-1 |

R=Unrestricted Read, W=Unrestricted Write, -n=Value after Reset

P0.7-0

**Port 0.** This port functions as a multiplexed address/data bus during external memory access, and as a general purpose I/O port on devices which incorporate internal program memory. During external memory cycles, this port will contain the LSB of the address when ALE is high, and data when ALE is low.

### **Stack Pointer (SP)**

|         | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|---------|------|------|------|------|------|------|------|------|

| SFR 81h | SP.7 | SP.6 | SP.5 | SP.4 | SP.3 | SP.2 | SP.1 | SP.0 |

|         | RW-0 | RW-0 | RW-0 | RW-0 | RW-0 | RW-1 | RW-1 | RW-1 |

R=Unrestricted Read, W=Unrestricted Write, -n=Value after Reset

**SP.7-0** Bits 7-0

**Stack Pointer.** This stack pointer identifies the location where the stack will begin. The stack pointer is incremented before every PUSH operation. This register defaults to 07h after reset.

## Data Pointer Low 0 (DPL)

|         | 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |

|---------|-------|-------|-------|-------|-------|-------|-------|-------|

| SFR 82h | PDL.7 | PDL.6 | PDL.5 | PDL.4 | PDL.3 | PDL.2 | PDL.1 | PDL.0 |

|         | RW-0  |

R=Unrestricted Read, W=Unrestricted Write, -n=Value after Reset

**DPL.7-0**Bits 7-0

**Data Pointer Low 0.** This register is the low byte of the standard 80C32 16-bit data pointer. DPL and DPH are used to point to non-scratchpad data RAM.

## Data Pointer High 0 (DPH)

|         | 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |

|---------|-------|-------|-------|-------|-------|-------|-------|-------|

| SFR 83h | DPH.7 | DPH.6 | DPH.5 | DPH.4 | DPH.3 | DPH.2 | DPH.1 | DPH.0 |

|         | RW-0  |

R=Unrestricted Read, W=Unrestricted Write, -n=Value after Reset

### **DPH.7-0** Bits 7-0

**Data Pointer High 0.** This register is the high byte of the standard 80C32 16-bit data pointer. DPL and DPH are used to point to non-scratchpad data RAM.

### **Data Pointer Low 1 (DPL1)**

|         | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |

|---------|--------|--------|--------|--------|--------|--------|--------|--------|

| SFR 84h | DPL1.7 | DPL1.6 | DPL1.5 | DPL1.4 | DPL1.3 | DPL1.2 | DPL1.1 | DL1H.0 |

|         | RW-0   |

R=Unrestricted Read, W=Unrestricted Write, -n=Value after Reset

**DPL1.7-0**

Bits 7-0

**Data Pointer Low 1.** This register is the low byte of the auxiliary 16-bit data pointer. When the SEL bit (DPS.0) is set, DPL1 and DPH1 are used in place of DPL and DPH during DPTR operations.

## Data Pointer High 1 (DPH1)

| Data    | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |

|---------|--------|--------|--------|--------|--------|--------|--------|--------|

| Pointer |        |        |        |        |        |        |        |        |

| High 1  |        |        |        |        |        |        |        |        |

| (DPH1)  |        |        |        |        |        |        |        |        |

| SFR 85h | DPH1.7 | DPH1.6 | DPH1.5 | DPH1.4 | DPH1.3 | DPH1.2 | DPH1.1 | DPH1.0 |

|         | RW-0   |

R=Unrestricted Read, W=Unrestricted Write, -n=Value after Reset

**DPH1.7-0** Bits 7-0

**Data Pointer High 1.** This register is the high byte of the auxiliary 16-bit data pointer. When the SEL bit (DPS.0) is set, DPL1 and DPH1 are used in place of DPL and DPH during DPTR operations.

## **Data Pointer Select (DPS)**

|         | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0    |

|---------|-----|-----|-----|-----|-----|-----|-----|------|

| SFR 86h | 0   | 0   | 0   | 0   | 0   | 0   | 0   | SEL  |

|         | R-0 | RW-0 |

R=Unrestricted Read, W=Unrestricted Write, -n=Value after Reset

Bits 7-0 Reserved. These bits will read 0.

SEL **Data Pointer Select.** This bit selects the active data pointer. Bit 0

0 = Instructions that use the DPTR will use PDL and PDH.

1= Instructions that use the DPTR will use PDL1 and PDH1.

20 of 175

| <b>Power Control (</b> | PCON) |

|------------------------|-------|

|------------------------|-------|

|         | 7      | 6     | 5 | 4 | 3    | 2    | 1    | 0    |

|---------|--------|-------|---|---|------|------|------|------|

| SFR 87h | SMOD_0 | SMOD0 | - | - | GF1  | GF0  | STOP | IDLE |

|         | RW-0   | RW-0  |   |   | RW-0 | RW-0 | RW-0 | RW-0 |

R=Unrestricted Read, W=Unrestricted Write, -n=Value after Reset

### SMOD 0 Bit 7

Serial Port 0 Baud Rate Doubler Enable. This bit enables/disables the serial baud rate doubling function for Serial Port 0.

0 = Serial Port 0 baud rate will be that defined by baud rate generation equation.

1 = Serial Port 0 baud rate will be double that defined by baud rate generation equation.

### **SMOD0**

Framing Error Detection Enable. This bit selects function of the Bit 6 SCON0.7 and SCON1.7 bits.

> 0 = SCON0.7 and SCON1.7 control the SM0 function defined for the SCON0 and SCON1 registers.

1 = SCON0.7 and SCON1.7 are converted to the Framing Error (FE) flag for the respective Serial Port.

Bits 5-4 Reserved. Read data is indeterminate.

### GF1 Bit 3

General Purpose User Flag 1. This is a general purpose flag for software control.

### GF<sub>0</sub> Bit 2

**General Purpose User Flag 0.** This is a general purpose flag for software control.

### **STOP** Bit 1

**Stop Mode Select.** Setting this bit will stop program execution, halt the CPU oscillator, and internal timers, and place the CPU in a low-power mode. This bit will always be read as a 0. Setting this bit while the Idle bit is set will place the device in an undefined state.

### **IDLE** Bit 0

Idle Mode Select. Setting this bit will stop program execution but leave the CPU oscillator, timers, serial ports, and interrupts active. This bit will always be read as a 0.

|                              |            |             |            |               |            | riigii-specu w | iciocontionei | Osci s Guide |  |

|------------------------------|------------|-------------|------------|---------------|------------|----------------|---------------|--------------|--|

| Timer/Counter Control (TCON) |            |             |            |               |            |                |               |              |  |

|                              | 7          | 6           | 5          | 4             | 3          | 2              | 1             | 0            |  |

| SFR 88h                      | TF1        | TR1         | TF0        | TR0           | IE1        | IT1            | IE0           | IT0          |  |

|                              | RW-0       | RW-0        | RW-0       | RW-0          | RW-0       | RW-0           | RW-0          | RW-0         |  |

|                              | R=Unrestri | icted Read, | W=Unrestri | cted Write, - | n=Value af | ter Reset      |               |              |  |

**Timer 1 Overflow Flag.** This bit indicates when Timer 1 overflows its TF1 maximum count as defined by the current mode. This bit can be cleared by Bit 7 software and is automatically cleared when the CPU vectors to the Timer 1 interrupt service routine.

0 =No Timer 1 overflow has been detected.

1 = Timer 1 has overflowed its maximum count.

TR1 **Timer 1 Run Control.** This bit enables/disables the operation of Timer 1.

Bit 6 0 = Timer 1 is halted.

1 = Timer 1 is enabled.

Timer 0 Overflow Flag. This bit indicates when Timer 0 overflows its TF<sub>0</sub> maximum count as defined by the current mode. This bit can be cleared by Bit 5 software and is automatically cleared when the CPU vectors to the Timer 0 interrupt service routine or by software.

0 =No Timer 0 overflow has been detected.

1 = Timer 0 has overflowed its maximum count.

TR<sub>0</sub> **Timer 0 Run Control.** This bit enables/disables the operation of Timer 0.

Bit 4 0 = Timer 0 is halted.

IT1

Bit 2

IE0

Bit 1

IT0

Bit 0

1 = Timer 0 is enabled.

IE1 **Interrupt 1 Edge Detect.** This bit is set when an edge/level of the type defined by IT1 is detected. If IT1=1, this bit will remain set until cleared in software or Bit 3 the start of the External Interrupt 1 service routine. If IT1=0, this bit will inversely reflect the state of the INT1 pin.

**Interrupt 1 Type Select.** This bit selects whether the INT1 pin will detect edge or level triggered interrupts.

0 = INT1 is level triggered.

1 = INT1 is edge triggered.

Interrupt 0 Edge Detect. This bit is set when an edge/level of the type defined by ITO is detected. If ITO=1, this bit will remain set until cleared in software or the start of the External Interrupt 0 service routine. If IT0=0, this bit will inversely reflect the state of the INTO pin

**Interrupt 0 Type Select.** This bit selects whether the INT0 pin will detect edge or level triggered interrupts.

0 = INT0 is level triggered.

1 = INT0 is edge triggered.

|         | 7    | 6                | 5    | 4    | 3    | 2    | 1    | 0    |

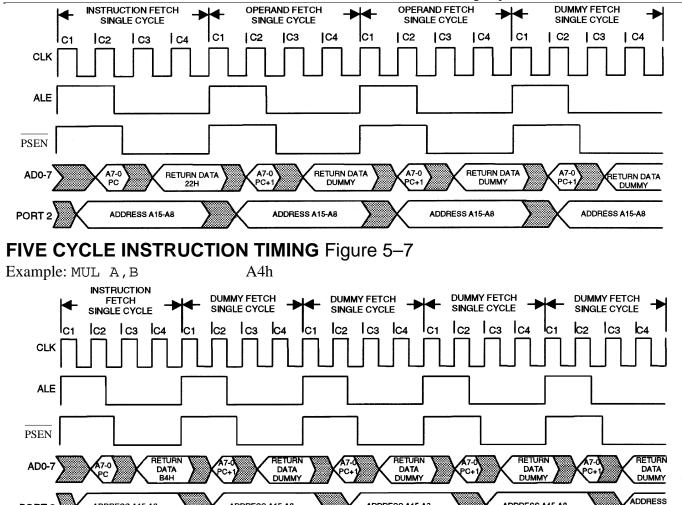

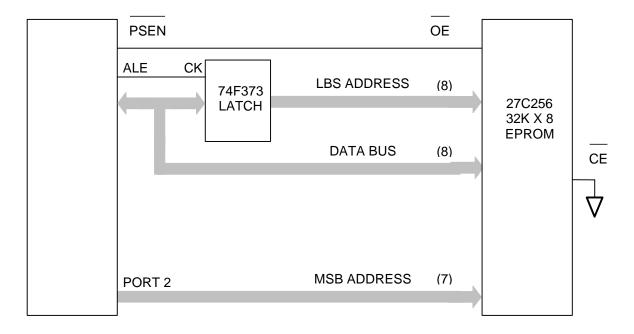

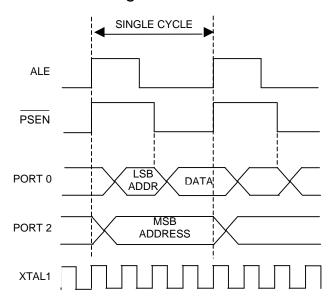

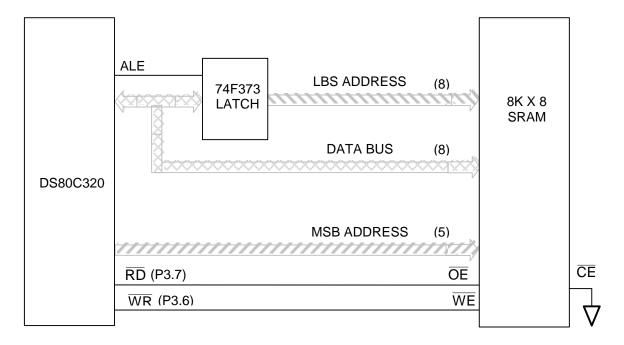

|---------|------|------------------|------|------|------|------|------|------|